嵌入式系統的PCIe時鐘分配

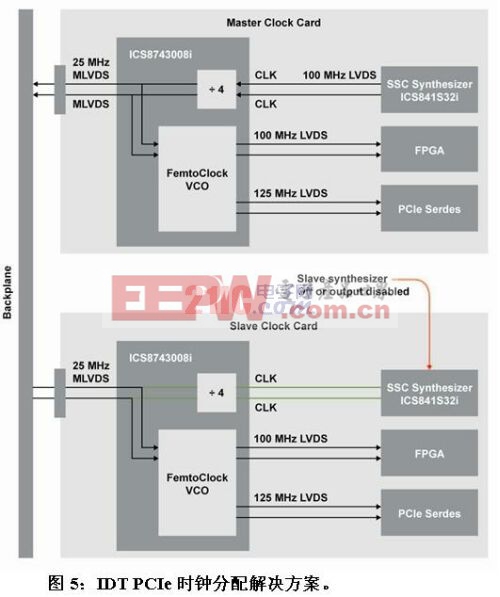

一個消除這些限制的解決辦法是降除主卡上的PCIe基準時鐘,并利用一個M-LVDS多點信號在背板之間進行分配,然后將其提高到目標卡所需的頻率。盡管理論上非常簡單,但實現PCIe抖動限制卻很棘手(見圖5,注意綠色信號線不起作用)。

這個解決方案可提供一個M-LVDS對,用來驅動或接收符合PCIe的基準時鐘。如圖5所示,在許多嵌入式系統中,根據應用的“與/或”插槽進行分配,每張卡都可作為主操作或端點操作。顯然,如圖5所示,只用于其中一種模式操作的卡將被簡化。系統中的一張卡將作為主卡,利用其板上晶振生成滿足PCIe限制的基準時鐘。

這個時鐘將利用內部時鐘分配網絡驅動所有板上PCIe器件。該時鐘也將到達非PLL除法器電路,將100MHz或125MHz向下降除為25MHz的背板頻率,然后將除降了的基準時鐘驅動到系統的其余卡上。系統中其它所有的卡將禁用板上時鐘發生器,形成基準時鐘線跡的三態驅動器,并接收來自背板的基準時鐘。隨后,這將通過基于PLL的ZDB提高到板上所需和分配的基準時鐘頻率,并將劃分了的基準時鐘驅動到系統的其它卡上。系統其它所有的卡將失去對板上時鐘發電器的使用,形成基準時鐘線跡三態驅動器,并接收來自背板的基準時鐘。這將通過基于PLL的ZDB提高到板上和分配所需的基準時鐘頻率。接收和提高來自背板的基準時鐘的電路通常在主卡上,如果需要,可以用來生成所需的另一個基準時鐘頻率。為了實現PCIe所需的低抖動,IDT FemtoClock PLL技術可用于時鐘合成器和ZDB。

這種設計的最主要難點在于,PLL雖然可以過濾掉頻率高于PLL本身環路帶寬的噪聲信號,但在低于PLL環路帶寬的低頻部分,卻增加了很多在調制頻率附近的附加抖動。另外,由于PLL無法完全跟蹤基準時鐘輸入的相位和頻率變化,所以將引起跟蹤偏移。像這種包含兩個以上用于頻率生成和轉換的級聯型PLL的背板PCIe方案必須謹慎對待,以盡量降低相位抖動和PLL跟蹤偏移。

PCIe抖動的測量

在深入分析這個解決方案的性能之前,需要先討論PCIe抖動性能的分析過程。PCIe抖動工作組關注的一個首要問題是確定一個恰當的基準時鐘。為實現這個目的,需要考慮基準時鐘的Tx和Rx PLL及相位插值器的過濾效果。同時,為避免對基準時鐘規格不足,這些PLL的峰值效應也需要考慮。這一過程分為四個主要步驟:

1.確定每個周期累積的相位誤差。串行數據傳輸不像并行數據傳輸那樣關心時鐘的Cycle-to-Cycle抖動和Period抖動,串行數據傳輸更關心累積相位誤。因此,我們必須首先確定每個時鐘周期的累積相位誤差。

2.將離散傅立葉變換(Discrete Fourier Transform,簡稱DFT)用于累積相位誤差數據,從而將時域的分析轉變到頻域進行分析。

3.將系統轉移函數用于累積相位誤差數據的DFT。

4.執行逆DFT,使過濾后的累積相位誤差數據轉回到時域內,這便是最終結果。

同時還要注意,通過設定系統轉移函數s=jω,可以在復雜的頻域實現PLL系統的過濾分析。該分析對連續系統很有用,但由于采用相位檢測器和反饋除法器等數字元件,大多數現代PLL方案不是純粹的模擬系統,因而z域數字分析會更精確。但是,PCI抖動工作組的初步研究表明,受s域分析影響的誤差最小,因此s域分析可用于建模。然而,當基頻低于PLL環路帶寬10倍時,s域近似值會顯著背離真值,所以系統設計師在選擇PLL時必須時刻謹記這一點。

有關這一過程的更多信息和背景資料,請查閱IDT應用筆記《PCIe基準時鐘要求》。

抖動測量技巧

測量方法不當很容易得到兩倍以上于正確方法的抖動測量值。這里有一些技巧:

1.從被測器件到示波器都使用屏蔽同軸電纜,并在示波器的輸入端做好恰當的匹配。

2.如果使用高阻抗探頭,可使用低電容探頭和接地夾,而非電線。

3.確保你使用了與樣本量一致的最高采樣率。

4.使示波器屏幕上的縱坐標最大,以便精確地測量電壓。

5.使顯示器、開關式電源和手機遠離被測器件。可行時使用線性電源。

6.當執行差分測量時,確保兩條電纜已經相互糾偏。

評論