嵌入式系統的PCIe時鐘分配

PCI Express(PCIe)是嵌入式和其它系統類型的背板間通信的一個非常理想的協議。然而,在嵌入式環境中,背板連接器引腳通常很昂貴,因此,采用點對點連接的星型結構的PCIe時鐘分配方案并不理想。本文將討論如何使用一個多點信號來分配PCIe時鐘,而且仍滿足PCIe第二代規范嚴格的抖動要求。

本文引用地址:http://www.104case.com/article/195478.htmPCIe計時

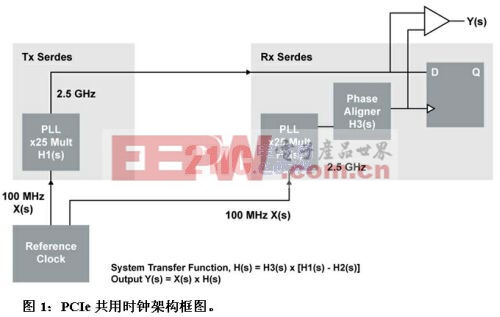

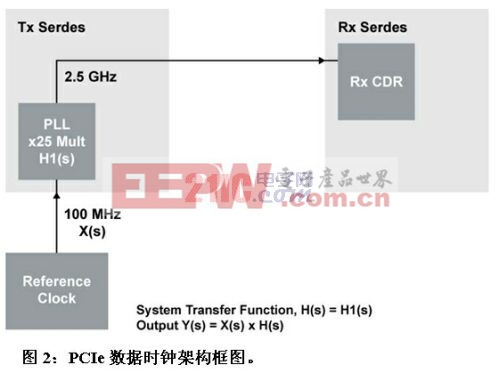

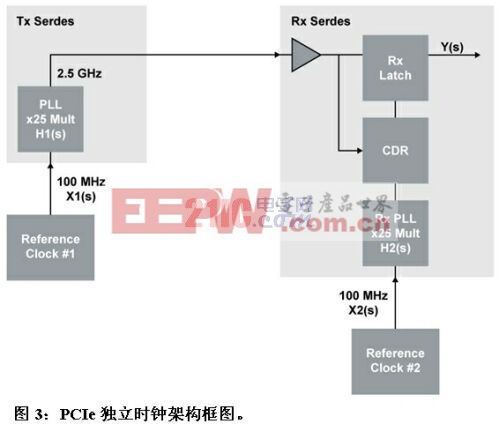

PCIe基本規范1.1和2.0為信令速率2.5Gbps和5.0Gbps的時鐘分配定義了三個不同模型,見圖1、圖2和圖3。

共用時鐘架構成為最常使用的方法有很多理由。首先,大多數支持PCIe接口的商用芯片只適用于這種架構。其次,這種架構是唯一可以直接支持展頻計時(Spread Spectrum clocking,簡稱SSC)的架構。SSC在減少電磁干擾峰化方面起著非常重要的作用,因此可以簡化符合系統電磁輻射限制的工作(圖4)。最后,這種架構最容易形成概念和設計。

評論