航天地面測試中1553B-PCI接口轉換技術實現

3.2 1553B 總線協議控制器的實現

1553B 總線協議控制器是本板卡構成的關鍵。市場上實現1553B 總線協議的芯片很多, 目前應用比較廣泛的是美國數據設備公司(DDC)的BU-61580,它雖然能夠完整的實現 1553B 總線協議,但缺點是設置比較復雜、體積比較大、功耗比較高。本設計采用Condor Engineering 公司的FlightCORE-1553 IP 核作為總線協議控制器,它完全滿足1553B 總線協 議,為主處理器和1553B 總線提供了完整、靈活的接口,能夠實現總線控制器(BC)、遠程 終端(RT)和總線監視器(BM)三種模式,并且適應ALTEA 和XILINX 大部分型號的FPGA, 與BU-61580 等協議芯片相比,具有使用靈活、功耗低、節省印制板面積等特點。

該總線控制器內部有 1K×16bits 的存儲空間,在存儲空間的低地址區是硬件寄存器、 固件保留區和文件寄存器,通過對這些寄存器的設置,可以方便地將控制器配置為BC、RT 或者BM。

下面對常用的寄存器進行說明: 1. 配置寄存器:用來選擇工作模式,即 BC、RT 或BM;

2. 控制寄存器:用來啟動相應的工作模式;

3. 中斷使能寄存器:設置產生中斷的條件;

4. 中斷狀態寄存器:當中斷產生時,固件將該寄存器相應位設置為有效,主處理器通 過讀該寄存器判斷是否有中斷發生;

5. 自檢寄存器:該寄存器具有只讀屬性,表明工作狀態。 實際應用中,該控制器需要4K 字的存儲空間才能正常工作,所以需要擴充存儲空間, 考慮到控制器接收處理總線數據后計算機能及時獲取而又不影響其正常工作,采用雙口RAM 比較合適,其中控制器前1K 字的存儲空間和雙口RAM 的地址空間是重疊的。

3.3 PCI 功能的實現

PCI 協議接口芯片采用PLX9054,通過XILINX 的FPGA 實現PLX9054 與1553 總線協議的 通信。當計算機啟動時,9054 需要串行EEPROM 為其提供一些必要的配置信息以實現對PCI 配置寄存器和本地寄存器的設置,這些信息除了局部空間的范圍和基地址外,還包括設備信 息和中斷資源等,這些需要我們事先燒寫到EEPROM 中,本文EEPROM 采用93LC56B。

實際應用中,需要根據存儲空間大小配置相應的9054 的地址空間,1553B 總線控制器 本身含有1K 字的寄存器空間,為了擴大存儲器空間,在FPGA 內例化了8K×16bits 的雙口 RAM。在9054 的本地端,將地址總線設為32 位,每一次32 位的讀寫操作僅對其低16 位進 行,高16 位未用,因此實際需要配置2 倍于雙口RAM 大小的空間,即32KByte,故EEPROM 中的局部地址空間0 范圍寄存器設為FFFF8000,局部地址空間0 描述寄存器設為4B430043。

3.4 PCI 總線和1553B 總線的橋接

在PCI 總線一邊,9054 的PCI 總線端需要和主機上的PCI 插槽進行連接。由于9054 是 專用的PCI 協議芯片,所以它的PCI 端可以直接通過插卡上的引線和PCI 插槽連接。

9054 的本地端和1553B 總線控制器HOST 端通過FPGA 實現邏輯轉換。9054 支持三種傳 輸模式,即主模式、從模式和DMA 模式,DMA 模式適合突發的大量數據的傳輸,由于1553B 總線的數據速率為1Mbps,數據量很小,因此采用從模式中的單周期讀寫模式,相對于主模 式而言電路設計和時序控制也相對簡單。

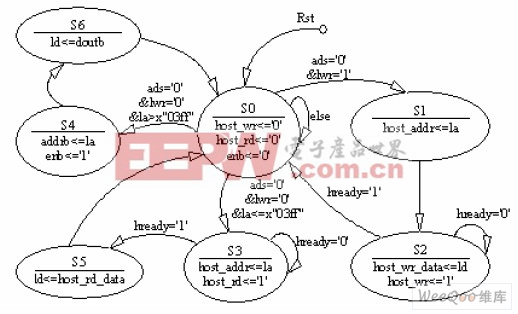

根據9054 從模式下單周期讀寫時序、1553B 總線控制器HOST 端時序和雙口RAM 時序采 用如圖2 所示的狀態機實現PCI 總線對1553B 總線控制器和雙口RAM 空間的讀寫操作。

圖2 狀態轉換圖

評論