DDR信號測量方法及信號完整性驗證面臨的挑戰(zhàn)與建議

3.1 利用前導(dǎo)寬度觸發(fā)器分離讀/寫信號

我們可以利用讀/寫前導(dǎo)的寬度來觸發(fā)示波器,實現(xiàn)讀/寫信號分離。根據(jù)JEDEC規(guī)范,讀前導(dǎo)的寬度為0.9到1.1個時鐘周期,而寫前導(dǎo)的寬度規(guī)定為大于0.35個時鐘周期,沒有上限。于是,我們在設(shè)置觸發(fā)條件之前,首先要確定讀/寫前導(dǎo)的寬度。由于讀前導(dǎo)和寫前導(dǎo)各自有不同的寬度,因此可利用這一點分離讀出的數(shù)據(jù)和寫入的數(shù)據(jù)。

但這種方法在使用過程中也存在問題。首先,JEDEC規(guī)范中對前導(dǎo)寬度的定義比較松散,而且不同ASIC/DRAM廠商在這方面的定義也不盡相同。此外,由于寫前導(dǎo)的上限沒有定義,因此它也有可能與讀前導(dǎo)寬度相同,而如果二者的值過于接近,那么要想分離讀信號與寫信號就十分困難了。

第二,如果寫前導(dǎo)的寬度為0.5個時鐘周期,與一個數(shù)據(jù)比特的寬度相當(dāng),那么硬件觸發(fā)器就無法區(qū)分寫前導(dǎo)比特與正常數(shù)據(jù)比特。

第三,隨著DDR數(shù)據(jù)率變高,時鐘周期將變得越來越窄。而隨著時鐘周期變窄,寫信號的前導(dǎo)寬度也會大幅縮小。以DDR3-1600為例,其最小前導(dǎo)寬度只有大約200ps。示波器的硬件觸發(fā)器有可能無法被如此窄的脈寬觸發(fā)。

3.2 利用更大的信號幅度觸發(fā)方法分離讀/寫信號

通常,讀/寫信號的信號幅度是不同的,因此我們可以通過在更大的信號幅度上觸發(fā)示波器來實現(xiàn)兩者的分離。然而,幅度更大的信號并不一定是讀信號或是寫信號,因此,我們雖然可以區(qū)分幅度更大的信號,但卻無法控制所分析的是讀信號還是寫信號。當(dāng)讀/寫信號幅度接近時則會發(fā)生類似的問題。

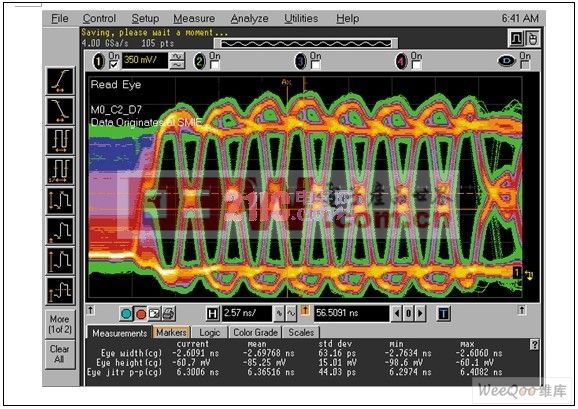

圖2:利用DQS信號的前導(dǎo)位觸發(fā)來分離讀/寫信號。

圖3:利用MSO實現(xiàn)控制信號觸發(fā)并分離讀/寫信號。

評論