基于虛擬儀器技術的雷達信號模擬器設計

2.2.2 程序設計

(1)主程序設計

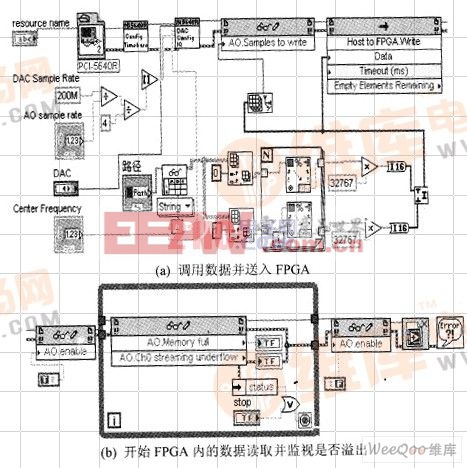

主程序的設計思路是:首先啟動 PCl-5640R板卡,然后調用仿真數據進行轉換,再將數據送入FPGA程序中處理,并不間斷地從FPGA讀取數據,以監控是否有溢出,最后判斷是否有錯誤,若有則中斷程序,如無則繼續監控是否有溢出和有無錯誤,程序如圖5所示。

圖5(a)是將仿真數據通過路徑控件讀入到主程序中,再轉換為16位數,然后通過Host to FPGA. Write控件將數據送入FPGA程序中。圖5(b)是先通過一個邏輯控件開始一個FPGA程序中的Case結構,該結構是用于數據讀取,然后通過一個for循環監視Memory是否溢出和數據是否送出到AO0口,并判斷是否停止,最后結束數據讀取并使FPGA停止工作。

(2)FPGA程序設計

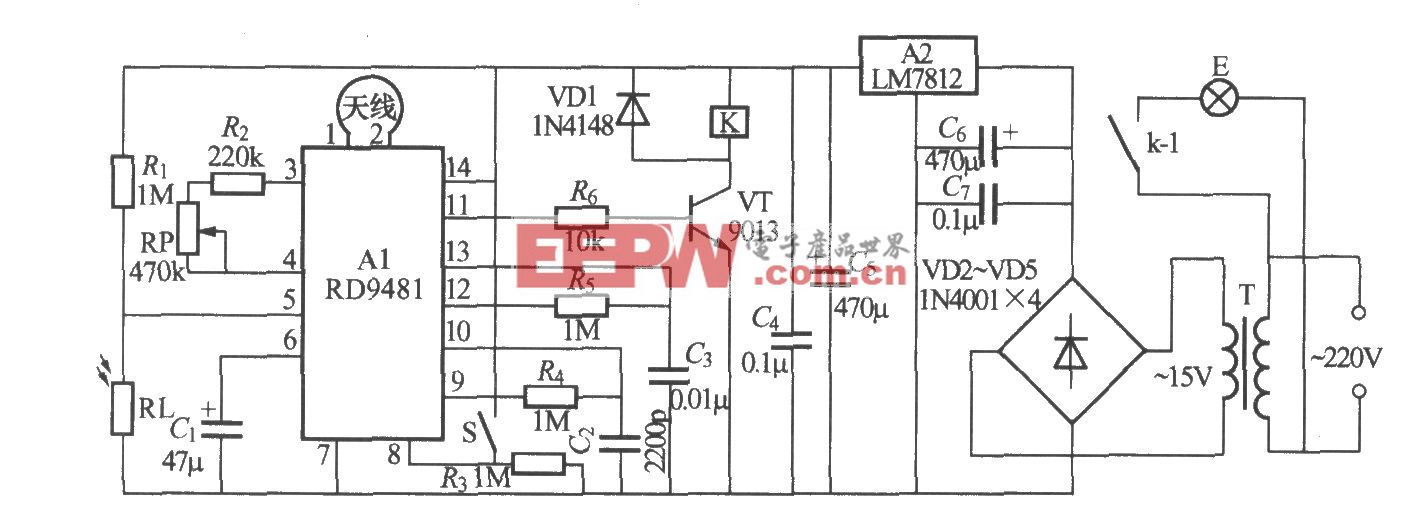

FPGA程序分為兩塊,一是在FPGA上設置A/D和D/A轉換功能;二是在FPGA上加存儲器,將數據通過FIFO存入存儲器Memory ,再通過FIFO將數據送入設置好的AO0口,進而將數據送出。FPGA程序設計如圖6所示。

圖5 主程序設計

圖6 FPGA程序設計

評論