基于AD9225的12位高速ADC的存儲電路設計與實現

AD9225輸出的12位數據,再加溢出指示位OTR共13位與兩片628512相連。兩片628512組成并聯結構,由同一地址發生器產生地址,同一寫信號線控制寫操作。20位地址發生器由五片同步計數器74161構成。注意,此處不能采用異步計數器,因為異步計數器的輸出延時太大。本文引用地址:http://www.104case.com/article/194401.htm

存儲器的存儲過程可以分解成三個過程來討論:① 地址碼加在RAM芯片的地址輸入端,選中相應的存儲單元,使其可以進行寫操作。② 將要寫入的數據放在數據總線上。③ 加上片選信號及寫信號,這兩個有效信號打開三態門,使DB上的數據進入輸入回路,送到存儲單元的位線上,從而寫入該存儲單元。

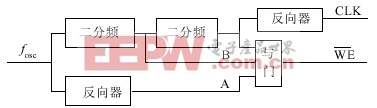

圖4所示的接口電路中,地址碼信息和數據碼信息在同一時鐘信號的上升沿產生,片選線由地址發生器的最高位(A19)提供。寫信號線是接口的最關鍵部分,它必須保證在AD9225轉換完成以后,在保持地址信息和數據信息不變的情況下,有足夠的低電平持續時間完成存儲操作。低速的數據采集系統可直接采用CLK作為寫信號。高速ADC在使用時,對時鐘的占空比要求很高。AD9225要求CLK的占空比在45%~55%之間,如果還直接采用CLK作為寫信號,將難以滿足要求。例如,如果采樣速率為10 Msps,CLK的低電平持續時間僅為50 ns,小于628512的存儲時間70 ns,因此,必須要對晶振信號進行適當的邏輯轉換以獲得足夠的寫周期。考慮到寫信號僅在低電平狀態有效,在產生信號時,可以盡量減少高電平的持續時間。經過多次仿真試驗,作者采用圖5所示的邏輯控制電路來獲得相應的寫信號。

圖5 邏輯控制電路

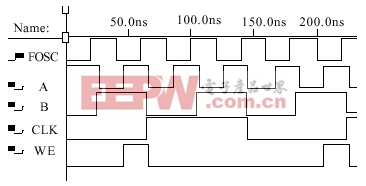

對應于此邏輯電路的時序如圖6所示。

圖6 邏輯控制電路時序圖

5 結論

本文詳細介紹了一種高 速A/D轉換芯片AD9225的結構和應用,在比較了各種高速數據采集系統的存儲方案的基礎上,給出了AD9225與628512存儲器的接口電路。該電路實際上是高速ADC與一般RAM接口的縮影。在寫信號的實現上,采用了控制邏輯,具有創新性和通用性。

電子血壓計相關文章:電子血壓計原理

評論