基于AD9225的12位高速ADC的存儲電路設計與實現

本文引用地址:http://www.104case.com/article/194401.htm

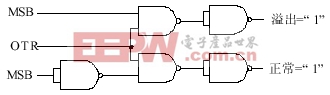

圖3 溢出和正常狀態的邏輯判斷圖

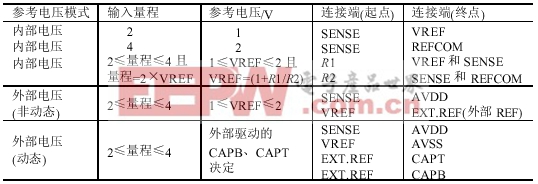

滿刻度量程= 2×VREF

VREF的值由SENSE引腳確定。如果SENSE與AVSS 相連,VREF是2.0 V,量程是0~4 V;如果SENSE與VREF直接相連, VREF是1.0 V,量程是0~2 V;如果SENSE與VREF通過電阻網絡相連,則VREF可以是1.0~2.0 V之間的任意值,量程是0~2VREF;如果SENSE與AVDD 相連,表示禁用內部參考源,即VREF由外部參考電壓源驅動。內部電路用到的參考電壓是出現在CAPT和CAPB端。表1是參考電壓和輸入量程的總結。

表1 參考電壓和輸入量程

在高速數據采集電路的實現中,有兩個關鍵的問題:一是模擬信號的高速轉換;二是變換后數據的存儲及提取。AD9225的采樣速度可達25Msps,完全可以滿足大多數數據采集系統的要求,故首要解決的關鍵問題是與存儲器的配合問題。 在數據采集電路中, 有以下幾種存儲方案可供選擇。

(1) 分時存儲方案

分時存儲方案的原理是將高速采集到的數據進行分時處理, 通過高速鎖存器按時序地分配給N個存儲器。雖然電路中增加了SRAM的片數,但使存儲深度增加,用低價格的SRAM構成高速數據存儲電路,獲得較高的(單位速度×單位存儲深度)/價格比。但由于電路單數據口的特點,不利于數據的實時處理,并且為使數據被鎖存后留有足夠的時間讓存儲器完成數據的存儲,需要產生特殊的寫信號線 。

(2)雙端口存儲方案

雙端口存儲器的特點是,在同一個芯片里,同一個存儲單元具有相同的兩套尋址機構和輸入輸出機構,可以通過兩個端口對芯片中的任何一個地址作非同步的讀和寫操作,讀寫時間最快達到十幾ns。當兩個端口同時(5 ns以內 )對芯片中同一個存儲單元尋址時, 芯片中有一個協調電路將參與協調。雙端口存儲器方案適用于小存儲深度、數據實時處理的場合。由于雙端口存儲器本身具備了兩套尋址系統,在電路的設計時,可以免去在數據存儲和讀取時對地址時鐘信號的切換問題的考慮,使數據變得簡單和快捷。

(3)先進先出存儲方案

先進先出存儲器的同一個存儲單元配備有兩個口:一個是輸入口,只負責數據的寫入;另一個是輸出口,只負責數據的輸出。先進先出(FIFO)存儲器方案適用于小存儲深度,數據需實時處理的場合。

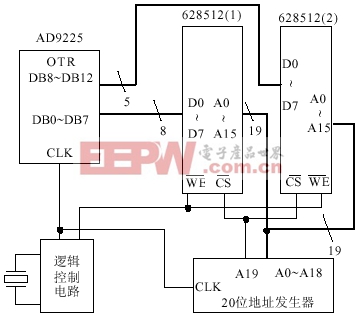

對用戶而言,存儲器的存儲速度和存儲容量是一對矛盾體:雙口RAM和FIFO可以實現很高的存儲速度,但其存儲容量難以滿足對大量數據存儲的需求;一般的靜態RAM雖然速度有限,但其存儲深度卻是雙口RAM和FIFO難以企及的,并且可以容易地實現多片擴展。對高速數據采集系統而言,由于采樣速率快、數據多,要求存儲深度比較大,實時處理的難度比較高,一般的靜態RAM就可以滿足速度要求。628512容量為512Kbit,存取時間70 ns,可以滿足10Msps以上的采樣要求,比較具有典型意義。圖4是AD9225與628512的接口電路圖,存儲方案實際是分時存儲的特例。

圖4 AD9225與628512的接口圖

電子血壓計相關文章:電子血壓計原理

評論