集成在半導體測試中的重要性

在今年5月1日于美國加利福尼亞州伯克利(Berkeley)舉行的2006年VLSI測試研討會上,一個專家小組探究了可測試設計(DFT)的發展前景。我們的姊妹出版物EDN的執行主編Ron Wilson報道說,討論的主要問題是單點工具或集成DFT是否最佳(參考文獻1)。參加討論的專家所代表的公司包括Cadence Design Systems、Mentor Graphics、Synopsys、SynTest和Virage Logic,他們一致認為:如欲建立DFT與設計工具、診斷工具、可制造性設計工具和ATE的聯系,那么集成將是不可或缺的。

本文引用地址:http://www.104case.com/article/193894.htm據Wilson報道,與會專家Sanjiv Taneja(Cadence公司負責Encounter Test產品線的副總裁)發表意見說:EDA行業是以一批單點工具起步的,而如今這些單點工具已經發展到了適合一種“包容型”架構(all-encompassing architecture)的水準。

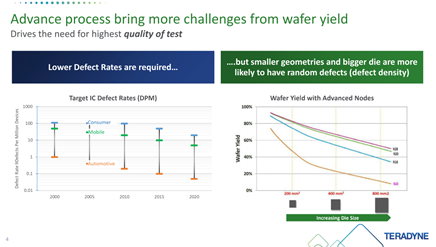

構筑一個用于解決設計、測試和成品率問題的包容型架構是Magma Design Automation公司的目標。該公司旨在利用其Talus平臺來實現采用65nm及更小工藝幾何尺寸制造的IC的快速設計,這被該公司描述為一個從RTL至輸出設計數據帶的“光刻實施流程”(lithography-aware implementation flow)。據Magma公司的一位高級市場主管Behrooz Zahiri稱,目前推出的是β版的Talus平臺,用于解決定時、區域、功耗、信號完整性、DFT和可制造性方面的問題。

當我向Zahiri問起該技術的有關情況時,他告訴我:Talus的主要特點之一是自動化程度有所提高。他把以往的EDA方法描述為“電子設計輔助”,為了把DFT、內置自檢(BIST)、線負載建模、平面規劃以及有可能以單點工具的形式存在的其他功能連接在一起,需要進行大量的腳本設計及其他的工作。他說:這樣的人工方法已呈難以為繼之勢,因為每項設計的投資金額將有可能從130nm工藝節點時的500萬美元攀升到45nm節點時的5000萬美元。

Zahiri說:最初將提供兩種版本的Talus,即:Talus LX和PX,它們分別面向邏輯和結構設計。他說:將針對可制造性和成品率學習進一步強化Talus。他表示,更多的細節信息在7月24日至28日于美國加利福尼亞州舊金山舉行的設計自動化會議上公布于眾。

不過,盡管有人在努力地把設計、測試和成品率控制組合成單一流程,但是,其他的替代方案也在接連面市。例如:Stratosphere Solutions公司剛剛首度推出了其StratoPro平臺,按照該公司首席戰略主管Prashant Maniar的說法,這個平臺是旨在“構建符合集中化市場需求的獨創技術”的工作成果的一部分,在此場合中,它抑制了由參量可變性所導致的成品率下降。另外,Incentia Design Systems公司最近公布了其TimeCraft軟件的一個新版本,該軟件是專為改善面向90nm和65nm設計的靜態時序分析的準確度和效率而設計的。

歸根結底,集成化的潮流是不可逆轉的,但是,旨在解決前沿工藝中出現的各種問題的新型工具同樣也會不斷涌現。

評論