使用Eye Doctor II工具分析解決測試著色難題

在信號完整性測試中,由于探測點受限引入的傳輸線延遲,及芯片的寄生參數,會導致測試波形在邊沿上有臺階或回溝。這種因測試引入的這種差異叫做測試著色,測試著色引入的信號質量問題一般不用解決,但如何分辨測試著色是一個難題。

本文引用地址:http://www.104case.com/article/192946.htmLeCroy公司高級信號完整性分析軟件包Eye Doctor II提供的VP@RCVR(接收端虛擬探測)功能可以非常方便地利用大家所熟悉的端接模型對這種測試難題進行分析,能夠簡單快速的分辨測試著色問題,提高硬件調試效率。

測試著色案例

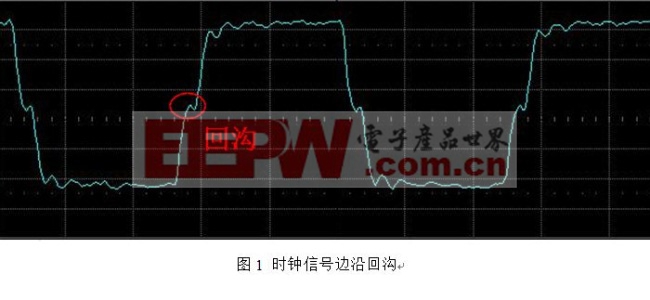

如下波形可以看到該時鐘信號邊沿出現回溝,這種現象隨著信號速率變高而越來越普遍,如何分析這種現象?我們可以通過仿真驅動芯片模型和電路拓撲,檢查PCB中參考平面的完整性、信號走線的間距來排除設計問題。如何進一步驗證分析是否是測試著色引入的?是否真正滿足芯片的指標要求?

下面以該問題作為案例介紹分析過程。

反射的基本原理分析

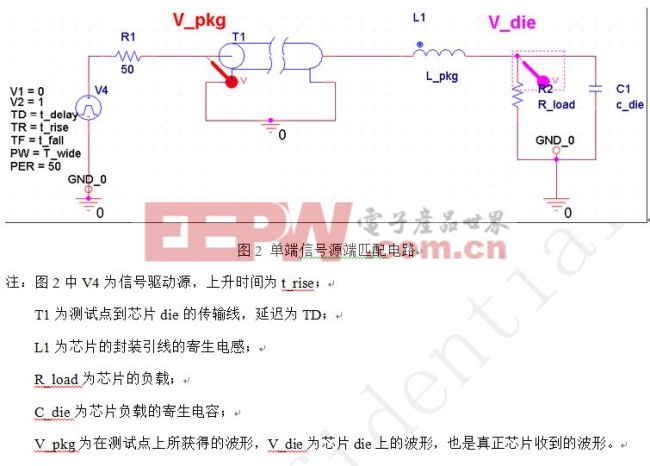

單端的時鐘信號以及邊緣敏感信號,常用源端串阻來吸收反射。這種拓撲設計理想狀況下,源端反射系數為0,負載端的反射系數為1。

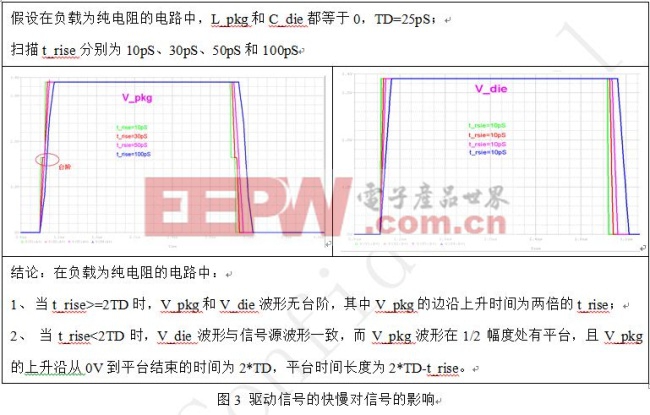

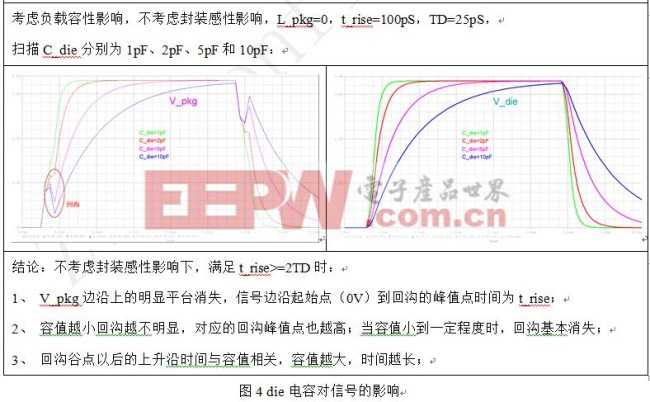

驅動信號的快慢t_rise對V_pkg和V_die的影響:

根據傳輸線的反射原理,當信號上升時間大于兩倍傳輸線延遲時,則在信號躍遷完成之前,信號探測點處會先完成發射疊加。因此當上升時間小于兩倍的傳輸線時延(TD)時,上升時間將對波形產生嚴重的影響。

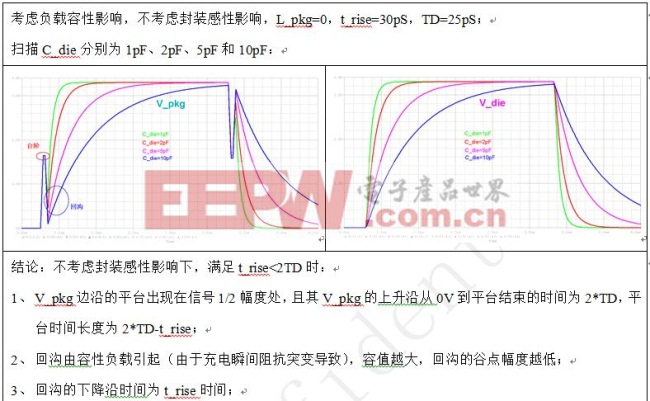

C_die的大小對V_pkg和V_die的影響:

而在實際系統中,幾乎沒有負載為純電阻的情況,比如:CMOS門電路的輸入大多是呈容性的,而封裝的焊接線和框架則是感性的。當傳輸線端接為容性負載時,驅動器和負載處的波形將與典型的傳輸線相應波形完全不同。本質上,電容是一種與時間有關的負載,當信號剛到達電容時,電容可看作短路負載,對應的反射系數為-1;電容充滿電后,可看作開路負載,對應的反射系數為1。

L_pkg的大小對V_pkg和V_die的影響:

當傳輸線上的電氣通路中出現串聯電感時,該電感同樣是與時間有關的負載。當電路中剛加上一個階躍電壓時,電感幾乎沒有電流流過,這會反射系數為1。電感的大小決定反射系數1能保持多長時間,如果電感足夠大,信號幅度將會倍增。此后電感釋放能量,其放電速度取決于LR電路的時間常數t=L/Z0(Z0為傳輸線阻抗)。

評論