使用先進(jìn)技術(shù)來(lái)加速SoC驗(yàn)證

摘要:近年來(lái),由于設(shè)計(jì)復(fù)雜度的增長(zhǎng),對(duì)于驗(yàn)證提出了更高的要求。驗(yàn)證環(huán)境變得越來(lái)越大,越來(lái)越復(fù)雜,設(shè)計(jì)和驗(yàn)證的雙重壓力導(dǎo)致仿真變得越來(lái)越慢。所有驗(yàn)證/仿真的速度已經(jīng)成為當(dāng)前SOC設(shè)計(jì)進(jìn)程中的重大挑戰(zhàn)。

本文引用地址:http://www.104case.com/article/192738.htm在我們的項(xiàng)目中,我們使用Synopsys的驗(yàn)證flow以及近年來(lái)Synopsys提供的新的方法/工具,比如性能分析工具來(lái)分析仿真瓶頸,使用分塊編譯來(lái)加速編譯,使用并行多核技術(shù)來(lái)加速編譯/運(yùn)行。使用UVM來(lái)增加環(huán)境的可復(fù)用性,等等,這些技術(shù)/特性的引入都大幅度加速了我們的仿真速度并減少了仿真時(shí)間。

項(xiàng)目以及驗(yàn)證環(huán)境介紹

我們的項(xiàng)目是GPU的項(xiàng)目,對(duì)于仿真性能有較高的要求,所以在項(xiàng)目中希望使用盡可能多的新技術(shù)來(lái)縮短仿真時(shí)間以及加速驗(yàn)證。

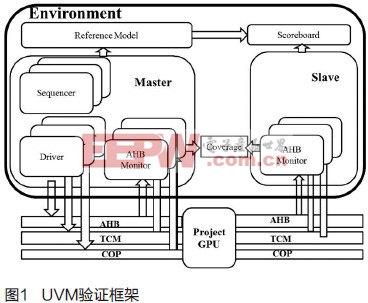

我們的驗(yàn)證環(huán)境使用UVM標(biāo)準(zhǔn)庫(kù)來(lái)搭建的。驗(yàn)證環(huán)境如圖1所示。

使用了Synopsys公司的VCS來(lái)作為我們的仿真工具。

工具版本:VCS 2012.09-SP1,Verdi 2013.04

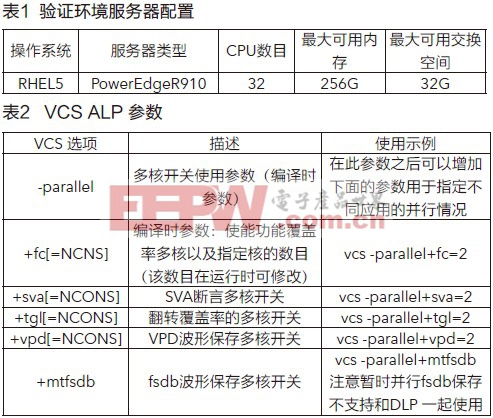

硬件環(huán)境如表1所示。

加速編譯的方法

隨著電路規(guī)模的不斷變大,編譯時(shí)間也成為了仿真過(guò)程中重要因素,如何加快/重用編譯數(shù)據(jù)庫(kù),是加速整個(gè)仿真過(guò)程不可缺少的部分。VCS提供了很多好的技術(shù)來(lái)加速編譯過(guò)程。

并行編譯

當(dāng)前基本上我們的服務(wù)器都能提供多核支持,并行編譯選項(xiàng)可以使用服務(wù)器的多核來(lái)提供更快的并行處理,來(lái)快速編譯生成數(shù)據(jù)庫(kù)。VCS并行編譯的選項(xiàng)如下:

-j[no_of_processes]

比如 vcs –j4 …,注意no_of_processes的數(shù)目不要超過(guò)實(shí)際可以提供的物理核數(shù)目。

評(píng)論