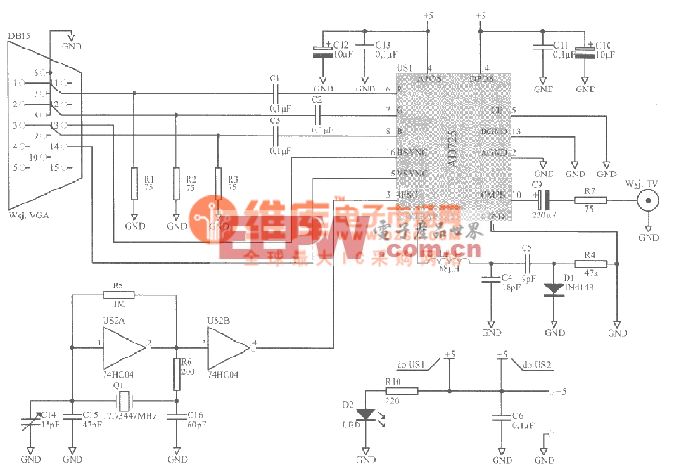

基于FPGA的VGA顯示控制器的設計

1.2.1 數據輸入緩沖模塊

數據輸入緩沖模塊為深度為1024、寬度為16bit的異步FIFO (先進先出),寫時鐘為DSP輸出的12MHZ的象素時鐘,讀時鐘為經時鐘鎖相環倍頻后的65MHZ的主時鐘,通過場下降沿檢測,來確保從一幀開始時接收數據。當輸入的原始圖像數據的行、場參考信號都有效時,該FIFO的寫使能有效,在輸入象素時鐘的同步下,開始接收數據,寫地址計數器為0到1023的循環計數器,當其計數到511或1023時,給主控制器發讀信號,主控制器隨后產生FIFO的讀使能信號,使讀使能信號在連續的512個讀時鐘周期內一直有效,即可連續讀出512個數據。由于讀時鐘頻率大于寫時鐘頻率,所以不會產生數據寫滿溢出的現象。本文引用地址:http://www.104case.com/article/192162.htm

1.2.2 主控制器模塊

該模塊為顯示控制器的主要控制部分,通過對輸入緩沖的讀請求信號和輸出緩沖的寫請求信號處理,來實現對兩個SDRAM的讀、寫切換。上電后,該模塊接收從輸入緩沖中讀出的數據并將其寫入到SDRAM 1中,同時從SDRAM2中讀出數據,送入到輸出緩沖中,當然最初讀出的數據為無效數據。當SDRAM1中寫滿一幀圖像數據,即1024×768個有效數據后,該模塊對兩個SDRAM進行讀、寫切換,即將接收數據寫入到SDRAM2中,同時從SDRAM 1中讀出數據,一直按此規則進行讀、寫切換。兩個SDRAM的讀、寫地址發生器靠主控制器內部的計數器來實現。

1.2.3 SDRAM控制器模塊

該模塊首先完成對SDRAM 的初始化,初始化過程為:上電后等待200 us,然后對所有BANK發預充命令,接著發出八個自動刷新命令,然后進行模式設置,模式設置時將SDRAM設置成連續的全頁并發模式,即512并發。

初始化結束后,SDRAM進入正常工作狀態,準備接收讀、寫命令。當SDRAM在空閑狀態下,為保持其數據不丟失,必須對其進行定時刷新,一般要求64ms內刷新4096次,通常根據時鐘頻率,用計數器計時鐘脈沖到15.625 us時,發自動刷新命令,但是當SDRAM在進行讀、寫進發時,自動刷新命令會打斷讀、寫,從而造成數據丟失。該設計中,由于在64ms內對SDRAM至少進行4096次讀、寫操作,所以可以不必對其進行刷新。

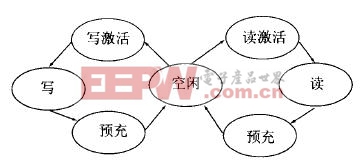

由于SDRAM被設置成全頁并發,預充命令可停止并發,所以當SDRAM讀、寫到511時,發出預充命令,來停止并發,同時關閉當前行,為下一次讀、寫作好準備。SDRAM初始化后,其狀態轉移圖如圖3所示。

圖3 SDRAM初始化后的狀態轉移圖

1.2.4 時序發生器模塊

該模塊為輸出行、場同步產生模塊,利用FPGA內部時鐘鎖相環倍頻后的65MHZ的主時鐘產生符合VESA標準的分辨率為1024×768、幀頻為60HZ的標準XGA格式的行、場同步信號,同時在行、場參考信號都有效時產生一個信號給輸出緩沖模塊,作為輸出緩沖的讀使能信號。根據VESA標準,分辨率為1024×768、幀頻為60HZ的標準XGA信號的象素時鐘為65MHZ,行同步信號的有效時間相當于1024個象素時鐘周期,同步頭寬度相當于136個象素時鐘周期,前肩寬度為相當于26個象素時鐘周期,后肩寬度為相當于162個象素時鐘周期。場同步信號的有效時間相當于768個行周期長度,同步頭為6個行周期長度,前肩為3個行周期長度,后肩為29個行周期長度。根據此標準,當行、場參考信號都有效時,一幅圖像可輸出1024×768個有效數據。該模塊的時序仿真波形如圖4所示。

1.2.5 輸出緩沖模塊

該模塊為深度為1024、寬度為16bit的異步FIFO(先進先出),寫時鐘和讀時鐘同為65MHZ的主時鐘,SDRAM初始化結束后,該模塊先從SDRAM2中讀出1024個數據,然后才使時序發生器模塊開始工作,當讀使能有效時,在讀時鐘同步下,讀地址計數器從0到1023循環計數,當計數器計到100或700時,該模塊向主控制器模塊發寫請求命令,從而每次可從SDRAM中連續讀出512個數據,由于在輸出行、場消隱期間,讀使能信號無效,所以,不會產生讀空現象。

1.2.6 色空間轉換模塊

輸出緩沖模塊輸出YCbCr(4:2:2)格式的信號,其輸出順序如表1所示。本設計采用臨近插值法,插值后的YCbCr格式如表2所示。

表1 YCbCr(4:2:2)圖像格式 Y0Cb0 Y1Cr0 Y2Cb2 Y3Cr2 Y4Cb4 Y5Cr4 ……

表2 插值后的YCbCr圖像格式 Y0Cb0Cr0 Y1Cb2Cr0 Y2Cb2Cr2 Y3Cb4Cr2 Y4Cb4Cr2 ……

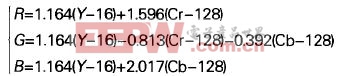

YCbCr色空間到RGB色空間的轉換公式為:

其中Y的范圍是(16,235),Cb、Cr的范圍是(16,240),為了防止相減后為負出現溢出,對轉換公式變形得:

用VHDL語言描述小數乘法時,通常是將小數擴大2的整數冪次方倍后,取整進行乘法運算,然后將結果進行移位操作。當需要對運算結果進行四舍五入時,可以在運算時加0.5,然后對運算結果取整。下面將對R的運算過程進行描述,運算精度取11位。

R=(1.164Y+1.596Cr)-222.912+0.5

= (1.164Y+1.596Cr)-222.412

= (1/211) [(2384Y+3296Cr)-455499]

將方括號中的運算結果右移11位,即可得到R的值。Cb、Cr的運算過程與此類似。

色空間轉換模塊輸出24bit RGB(8:8:8)信號,該信號經D/A轉換后,配合時序發生器模塊產生的行、場同步信號,即可在VGA顯示器上顯示。

色空間轉換模塊之所以放在輸出緩沖模塊后,主要是為了減少輸入緩沖和輸出緩沖模塊中的先進先出及SDRAM的存儲空間,如在相同精度下,SDRAM存儲一幀圖像將會占用1024×768×24bit的存儲空間,色空間轉換模塊放在輸出緩沖模塊后,將會減少1/3的存儲空間。

2 顯示控制器的硬件實現

該顯示控制器是基于Xilinx公司的Spartan-IIE系列FPGA XC2S300E-6-PQ208C設計實現的。此FPGA邏輯資源豐富,其內有30萬個系統門,6912個邏輯單元(LC),1536個可配置邏輯快(CLB),64Kbit的塊RAM,146個可用的I/O口,4個數字延遲鎖相環(DLL)。塊RAM可實現大量數據的內部存儲,延遲鎖相環可對時鐘進行管理,可自動調整并消除輸入時鐘與FPGA內部時鐘之間的相位偏移,同時還可實現對時鐘的分頻、倍頻和移相。

用于幀緩存的兩個SDRAM 的型號為HY57V281620HCST,此SDRAM 為Hynix公司生產的高速存儲器,其內有四個Bank,每個Bank的存儲空間為2M×16bit,可應用于需存儲大量數據的場合。

3 結論與展望

本文設計的顯示控制器具有很強的靈活性,當輸入圖像格式改變時,只需在色空間轉換模塊做相應修改,便可實現不同格式圖像的VGA顯示。基于該顯示控制器而研發的高分辨率監控攝像機、數字視頻展臺等產品可廣泛應用在教育、銀行、煤礦、交通、醫療等領域。

評論