PCB布線要點(diǎn)

一.電路板設(shè)計(jì)步驟

本文引用地址:http://www.104case.com/article/192159.htm 一般而言,設(shè)計(jì)電路板最基本的過(guò)程可以分為三大步驟。

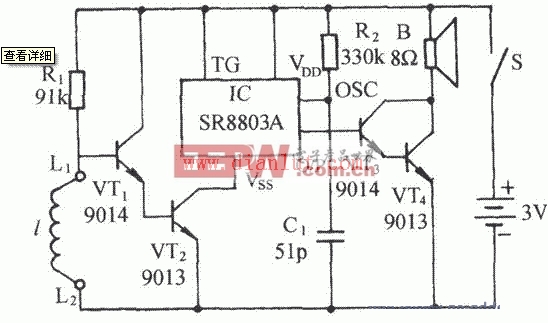

(1). 電路原理圖的設(shè)計(jì): 電路原理圖的設(shè)計(jì)主要是PROTEL099的原理圖設(shè)計(jì)系統(tǒng)(Advanced Schematic)來(lái)繪制一張電路原理圖。在這一過(guò)程中,要充分利用PROTEL99所提供的各種原理圖繪圖工具、各種編輯功能,來(lái)實(shí)現(xiàn)我們的目的,即得到一張正確、精美的電路原理圖。

(2). 產(chǎn)生網(wǎng)絡(luò)表: 網(wǎng)絡(luò)表是電路原理圖設(shè)計(jì)(SCH)與印制電路板設(shè)計(jì)(PCB)之間的一座橋梁,它是電路板自動(dòng)的靈魂。網(wǎng)絡(luò)表可以從電路原理圖中獲得,也可從印制電路板中提取出來(lái)。

(3). 印制電路板的設(shè)計(jì): 印制電路板的設(shè)計(jì)主要是針對(duì)PROTEL99的另外一個(gè)重要的部分PCB而言的,在這個(gè)過(guò)程中,我們借助PROTEL99提供的強(qiáng)大功能實(shí)現(xiàn)電路板的版面設(shè)計(jì),完成高難度的等工作。

二.繪制簡(jiǎn)單電路圖

2.1 原理圖設(shè)計(jì)過(guò)程原理圖的設(shè)計(jì)可按下面過(guò)程來(lái)完成。

(1)設(shè)計(jì)圖紙大小 Protel 99/ Schematic后,首先要構(gòu)思好零件圖,設(shè)計(jì)好圖紙大小。圖紙大小是根據(jù)電路圖的規(guī)模和復(fù)雜程度而定的,設(shè)置合適的圖紙大小是設(shè)計(jì)好原理圖的第一步。

(2)設(shè)置Protel 99/Schematic設(shè)計(jì)環(huán)境 設(shè)置Protel 99/Schematic設(shè)計(jì)環(huán)境,包括設(shè)置格點(diǎn)大小和類型,光標(biāo)類型等等,大多數(shù)參數(shù)也可以使用系統(tǒng)默認(rèn)值。

(3)旋轉(zhuǎn)零件 用戶根據(jù)電路圖的需要,將零件從零件庫(kù)里取出放置到圖紙上,并對(duì)放置零件的序號(hào)、零件封裝進(jìn)行定義和設(shè)定等工作。

(4)有原理圖布線 利用Protel 99/Schematic提供的各種工具,將圖紙上的元件用具有電氣意義的導(dǎo)線、符號(hào)連接起來(lái),構(gòu)成一個(gè)完整的原理圖。

(5)調(diào)整線路 將初步繪制好的電路圖作進(jìn)一步的調(diào)整和修改,使得原理圖更加美觀。

(6)報(bào)表輸出 通過(guò)Protel 99/Schematic提供的各種報(bào)表工具生成各種報(bào)表,其中最重要的報(bào)表是網(wǎng)絡(luò)表,通過(guò)網(wǎng)絡(luò)表為后續(xù)的電路板設(shè)計(jì)作準(zhǔn)備。

(7)文件保存及打印輸出 最后的步驟是文件保存及打印輸出。

單片機(jī)控制板的設(shè)計(jì)原則需要遵循的原則如下:

(1) 在元器件的布局方面,應(yīng)該把相互有關(guān)的元件盡量放得*近一些,例如,時(shí)鐘發(fā)生器、晶振、CPU的時(shí)鐘輸入端都易產(chǎn)生噪聲,在放置的時(shí)候應(yīng)把它們近些。對(duì)于那些易產(chǎn)生噪聲的器件、小電流電路、大電流電路開(kāi)關(guān)電路等,應(yīng)盡量使其遠(yuǎn)離單片機(jī)的邏輯控制電路和存儲(chǔ)電路(ROM、RAM),如果可能的話,可以將這些電路另外制成電路板,這樣有利于抗干擾,提高電路工作的可*性。

(2) 盡量在關(guān)鍵元件,如ROM、RAM等芯片旁邊安裝去耦電容。實(shí)際上,印制電路板走線、引腳連線和接線等都可能含有較大的電感效應(yīng)。大的電感可能會(huì)在Vcc走線上引起嚴(yán)重的開(kāi)關(guān)噪聲尖峰。防止Vcc走線上開(kāi)關(guān)噪聲尖峰的唯一方法,是在VCC與電源地之間安放一個(gè)0.1uF的電子去耦電容。如果電路板上使用的是表面貼裝元件,可以用片狀電容直接緊*著元件,在 Vcc引腳上固定。最好是使用瓷片電容,這是因?yàn)檫@種電容具有較低的靜電損耗(ESL)和高頻阻抗,另外這種電容溫度和時(shí)間上的介質(zhì)穩(wěn)定性也很不錯(cuò)。盡量不要使用鉭電容,因?yàn)樵诟哳l下它的阻抗較高。在安放去耦電容時(shí)需要注意以下幾點(diǎn):

在印制電路板的電源輸入端跨接100uF左右的電解電容,如果體積允許的話,電容量大一些則更好。

原則上每個(gè)集成電路芯片的旁邊都需要放置一個(gè)0.01uF的瓷片電容,如果電路板的空隙太小而放置不下時(shí),可以每10個(gè)芯片左右放置一個(gè)1~10的鉭電容。

對(duì)于抗干擾能力弱、關(guān)斷時(shí)電流變化大的元件和RAM、ROM等存儲(chǔ)元件,應(yīng)該在電源線(Vcc)和地線之間接入去耦電容。

電容的引線不要太長(zhǎng),特別是高頻旁路電容不能帶引線。

(3) 在單片機(jī)控制系統(tǒng)中,地線的種類有很多,有系統(tǒng)地、屏蔽地、邏輯地、模擬地等,地線是否布局合理,將決定電路板的抗干擾能力。在設(shè)計(jì)地線和接地點(diǎn)的時(shí)候,應(yīng)該考慮以下問(wèn)題:

邏輯地和模擬地要分開(kāi)布線,不能合用,將它們各自的地線分別與相應(yīng)的電源地線相連。在設(shè)計(jì)時(shí),模擬地線應(yīng)盡量加粗,而且盡量加大引出端的接地面積。一般來(lái)講,對(duì)于輸入輸出的模擬信號(hào),與單片機(jī)電路之間最好通過(guò)光耦進(jìn)行隔離。

在設(shè)計(jì)邏輯電路的印制電路版時(shí),其地線應(yīng)構(gòu)成閉環(huán)形式,提高電路的抗干擾能力。

地線應(yīng)盡量的粗。如果地線很細(xì)的話,則地線電阻將會(huì)較大,造成接地電位隨電流的變化而變化,致使信號(hào)電平不穩(wěn),導(dǎo)致電路的抗干擾能力下降。在布線空間允許的情況下,要保證主要地線的寬度至少在2~3mm以上,元件引腳上的接地線應(yīng)該在1.5mm左右。

評(píng)論