基于FPGA的線陣CCD驅動時序及 模擬信號處理的設計

4.2 AD9826時序設計及仿真

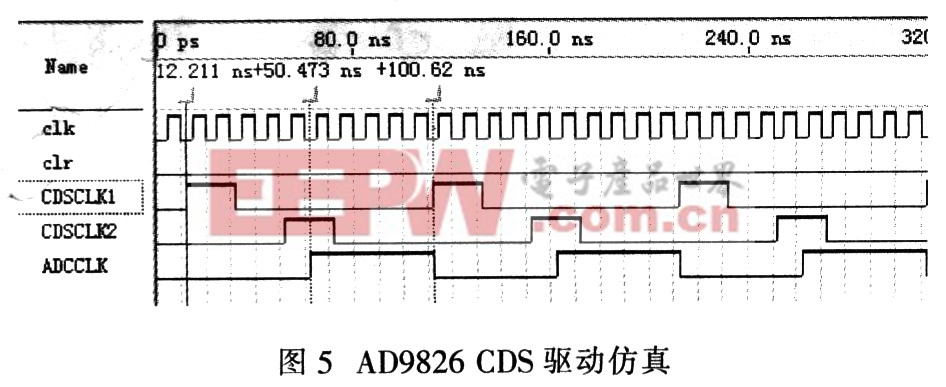

通過對AD9826單通道CDS采樣時序分析,結合TCDl501D輸出信號的特點,設計出正確合理的CDS驅動時序是保證該器件正常工作的基礎。充分利用硬件編程語言(VHDL)的優點,產生各項時序。依據TCDl501D輸出信號OS的時序要求及AD9826對CDS的要求,可設定各脈沖的參數為:主時鐘為100 MHz,CDSCLK1=CDSCLK2=10 MHz,占空比為l:4,兩次采樣間隔為40 ns,均為下降沿采樣;AD―CCLK=10MHz,占空比為1:l,低電平有效。編譯后通過波形仿真的結果如圖5所示,其中12.211 ns線為基準,+100.62ns線為相對基準線的偏移量,可知CDSCLKl周期為100 ns,滿足器件手冊中所規定的要求。

5 結語

通過對TCDl50lD輸出圖像信號特征的簡要分析,分別闡述了內、外2種除噪方法,并給出了相應的時序,再利用Quartus II 7.2軟件平臺對TCDl501D CCD驅動時序及AD9826的采樣時序進行了設計及結果仿真,使CCD的驅動變得簡單且易于處理,這是傳統邏輯電路無法比擬的,對其他CCD時序驅動及后續處理提供了一定的參考價值。

評論