基于FPGA 的簡化UART 電路設計

發送模塊主要實現對并行數據的緩存,并串轉換,然后把串行數據按照既定數據幀格式進行輸出,其機構如圖3 所示:

圖3 UART 發送模塊

a) data_input[7:0]是8 位并行數據的輸入端,轉換成串行數據后從txd 輸出;

b) wrn 是寫控制信號,為1 時禁止數據輸入,為0 時允許輸入;

c) reset 為系統復位輸入端,低電平有效;

d) clk 為系統時鐘信號輸入端,由波特率發生器產生;

e) tser 是并串轉換過程的標志:在沒有數據轉換時保持為1,在并串轉換開始時變成0,

并在轉換過程中保持為0; f) tbre 是整個工作過程的標志。實驗中串行數據結構為1 位起始位,8 位數據位,1 位奇偶校驗位,1 位停止位。數據 的發送由外部接收模塊控制,接收模塊給出wrn 信號,UART 發送模塊根據此信號將并行數據data-input 鎖存進發送緩沖,并通過移位寄存器進行并串轉換,在轉換結束后加上奇偶校驗位,發送到端口txd 進行串行輸出。在整個工作過程中,輸出信號tbre 作為標志信號,在串行數據全部輸出完畢之后變成0, 并在發送模塊未工作時保持為0。

2.4 接收模塊

接收模塊的結構如圖4 所示。接收模塊的作用是把收到的串行數據轉換成并行數據進行輸出,并判斷收到數據是否有錯。接收模塊的內部結構及工作過程與發送模塊類似,只不過接收模塊的工作和發送模塊的工作相反,是進行數據的串并轉換。

圖4 UART 接收模塊

a) rxd 接收串行數據輸入;

b) rdn 為輸入控制端,只有rdn 為0 時,并行數據才允許輸出;

c) data-ready 為數據是否準備好的標志;

d) parity-error 為校驗位是否出錯的標志;

e) framing-error 為幀是否出錯的標志;

f) data-out[7:0]為并行數據輸出端。

接收模塊從捕捉到數據串的第一個0 開始工作,然后把隨后依次輸入的8 個數據位通過移位在寄存器中完成竄并轉換,并將并行數據輸出至端口data-out 。將8 個數據位移位至寄存器后,接收模塊將檢測輸入數據串的最后一位是否為1(停止位)來判斷接收到的數據幀是否出錯,若不為1,就將輸出framing-error 置1。

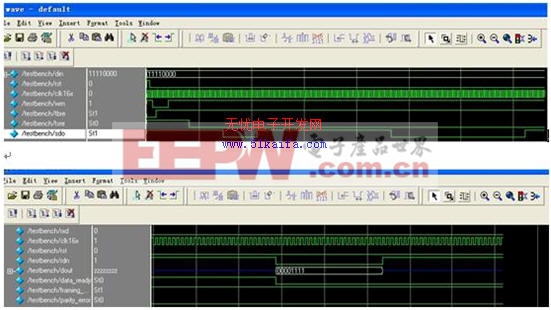

3 仿真驗證在實驗中,作者選用Altera 公司的Cyclone 系列產品中的EP1C12Q240C8 芯片,硬件描述語言采用Verilog HDL,用Quartus 5.1 進行邏輯綜合,仿真工具則使用ModelSim6.0 。發送模塊和接收模塊的仿真結果分別如圖5 所示。發送的數據能夠嚴格按照串行通信協議進行傳輸;接收的數據也完全正確。通過仿真測試后,將程序下載到FPGA 芯片中運行,結果通信數據正確,電路工作穩定、可靠。

圖5 發送和接收模塊仿真

4 結束語

用FPGA 實現了UART 通信功能,可以實現對數據的接收和發送,并可以在接收 數據時對其校驗位、停止位進行判斷,在發送數據時可以形成完整的一幀數據格式。本 文利用FPGA 設計實現了UART 的核心功能,可以和上位機進行異步串行通信。實驗 證明該UART 設計占用資源少,工作穩定可靠。

本文作者創新觀點:本文對UART 系統結構進行了模塊化分析,可以根據實際的需要可選擇地實現相應的通信功能,簡化了電路設計,提高了系統的可靠性,可以靈活地嵌入到各個通信系統當中。

評論