基于DSP Builder的正弦信號源優化設計及其FPGA實現

本文引用地址:http://www.104case.com/article/192111.htm

本文引用地址:http://www.104case.com/article/192111.htm3 信號源的FPGA實現

Matlab/Simulink對設計好的DDS系統進行編譯,通過調用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ的工程文件,再調用QuartusⅡ完成綜合、網表生成和適配,直至完成FPGA的配置下載過程。

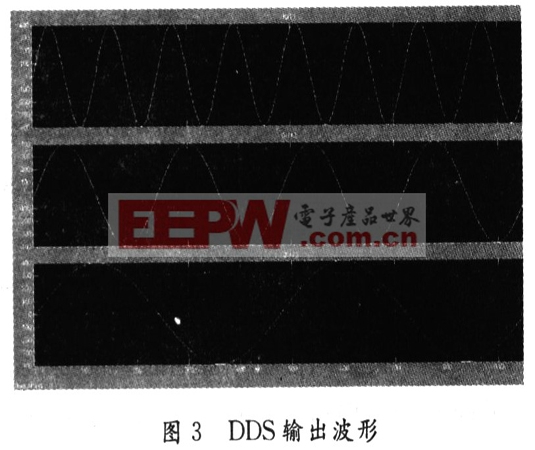

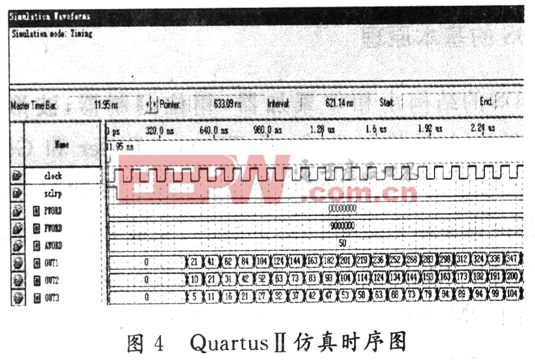

本設計方案采用的FPGA芯片是APEX20K系列器件EP20K200FC484。所得結果中的數字輸出可以輸出到SRAM芯片中,然后上載到計算機進行數字信號分析,模擬輸出則通過HP示波器測試。圖4給出了用QuartusII的仿真結果。圖中,clock為系統時鐘,sclrp為高電平復位信號,PWORD,FWORD,AWORD的值分別設為十進制數0,9000000和50。仿真得到的3個輸出OUTl,OUT2和OUT3與Matlab/Simulink中的仿真結果在相位、頻率和幅度上基本一致。實驗表明,利用FPGA所計設的DDS在滿足性能的條件下,節約了芯片資源,提高了輸出的精度。

4 結語

本文介紹了一種改進了的基于DSP Builder的正弦信號發生器設計方法,應用APEX20K系列FPGA芯片實現。繼承了傳統DDS設計中調頻、調相迅速的優點,同時,采用了查找表壓縮方案,使芯片在節約資源的基礎上達到了較高的輸出精度。

評論