基于PCI總線和CPLD的任意信號發生器設計

CPLD在系統中的主要作用是用來將PCI控制器傳輸過來的數據,經過一定的算法處理,得到DDS外圍管腳的狀態及向DDS中寫入控制寄存器數值,使DDS根據配置信息產生所需要的信號。

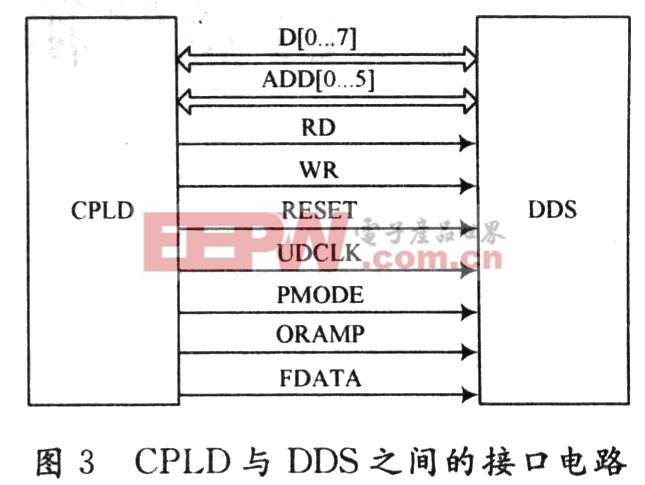

本設計中使用的CPLD是Altera公司的7000S系列,工作電壓為5 V,具有192個宏單元,采用通用JTAG方式下載。CPLD與DDS之間的接口電路主要包括8位數據線D[7:O]。6位地址線ADD[5:0],串并選擇信號PMODE,復位信號RESET,外部更新信號UDCLK、讀寫信號WR、RD和控制信號0RAMP、FDATA。如圖3所示。本文引用地址:http://www.104case.com/article/192108.htm

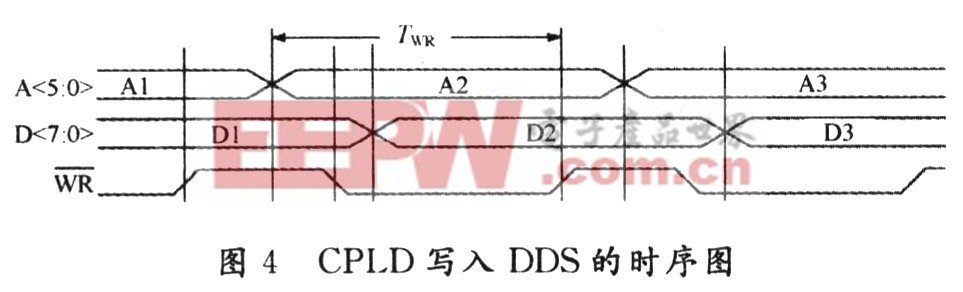

考慮到DDS信號輸出的實時性和減少CPLD的宏單元的占用,本設計中使用9052的IOWR#信號去觸發DDS的寫入信號WR。DDS控制寄存器的寫入方式有串行和并行兩種,由PMODE管腳控制,當PMODE信號為高時,為并行寫入模式,當PMODE信號為低時,為串行工作模式。由于設計中PCI9052寫入CPLD的數據為8位并行輸入,所以在這里選用了并行的方式向DDS的控制寄存器中寫入數據。寫入的時序如圖4所示。

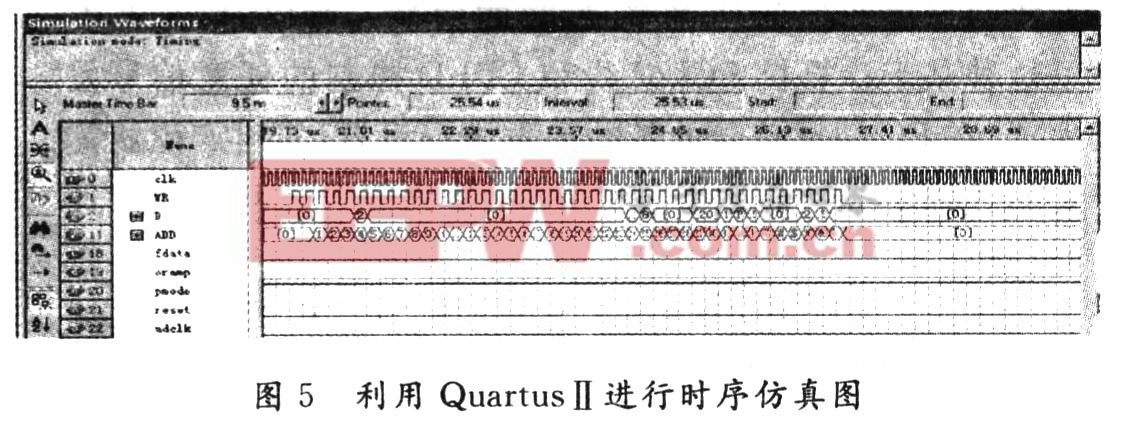

CPLD的程序在Altera公司提供的QuartusⅡ開發系統下通過Verilog HDL語言來實現。在QuartusⅡ環境中,可以方便地對波形進行仿真,便于查看和修改程序中可能存在的問題。QuartusⅡ仿真環境如圖5所示。

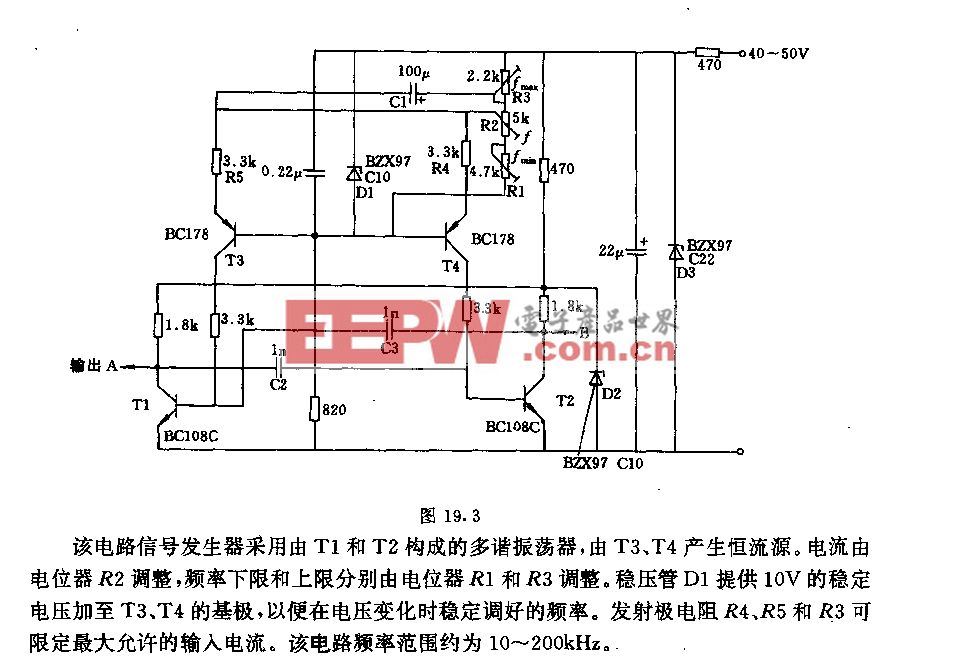

2.3 DDS輸出部分設計

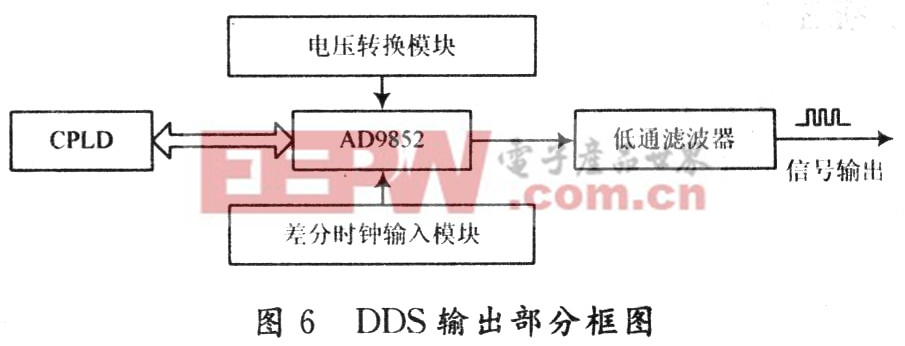

DDS部分電路設計除了與CPLD之間的連接電路外,還有DDS的外圍電路設計。本系統中DDS的外圍電路主要包括電壓轉換、差分時鐘信號輸入和低通濾波器三個部分,如圖6所示。設計中的DDS采用的是AD公司的通用DDS芯片AD9852,芯片的工作電壓為3.3 V,最高系統時鐘為300 MHz。

在整個系統中,PCI9052和CPLD的工作電壓為5 V,所以需要將工作電壓由5 V轉換為DDS正常工作的3.3 V,設計中采用了專用的電壓轉換模塊,完成電壓轉換工作,為DDS及其外圍電路提供3.3 V工作電壓。

差分時鐘輸入模塊是為了DDS輸出信號能夠得到較好頻譜純凈度,本設計采用了20 MHz的有源晶振,通過MCl00LVEL16D芯片產生20 MHz的差分時鐘信號,作為DDS的外部輸入時鐘。

為了濾去不需要的頻率成分和抑制輸出信號的雜散,在信號的輸出部分,采用了一個π型結構的LC低通濾波器,濾波器的結構圖如圖7所示。

評論