基于DDS技術(shù)的多路同步信號源的設(shè)計

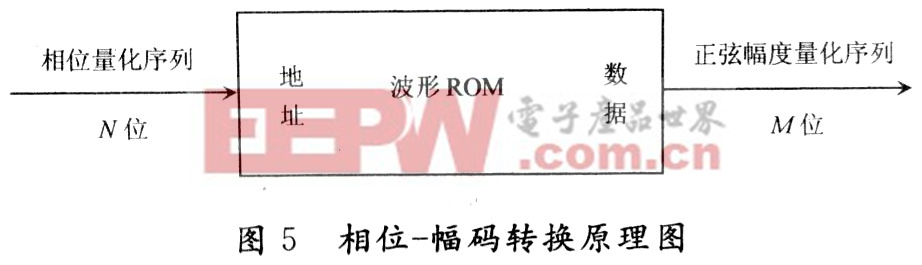

用相位累加器輸出的數(shù)據(jù)作為波形存儲器的取樣地址,進(jìn)行波形的相位一幅碼轉(zhuǎn)換,即可在給定的時間上確定輸出的波形的抽樣幅碼。本設(shè)計利用FPGA資源,構(gòu)造一個10位的ROM進(jìn)行數(shù)據(jù)的存儲和轉(zhuǎn)換。本文引用地址:http://www.104case.com/article/192052.htm

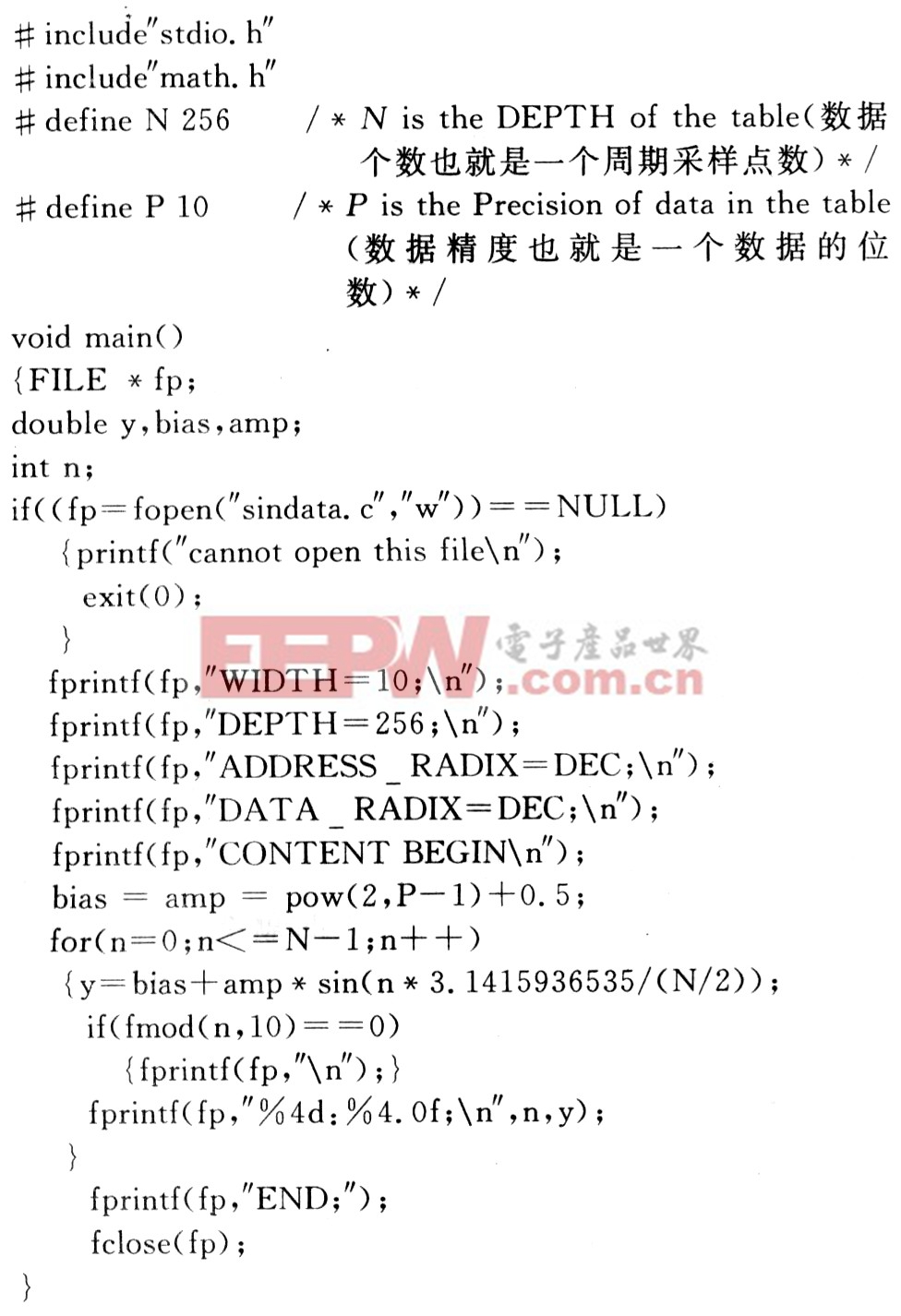

ROM可利用Quartus的插件管理程序Megawiz-ard plug-in manager容易獲得,這里給出正弦波形數(shù)據(jù)生成的C程序,來生成ROM存儲的數(shù)據(jù)。要想生成其他波形的數(shù)據(jù),只需要簡單修改其中的波形表達(dá)式即可。

3 仿真與調(diào)試

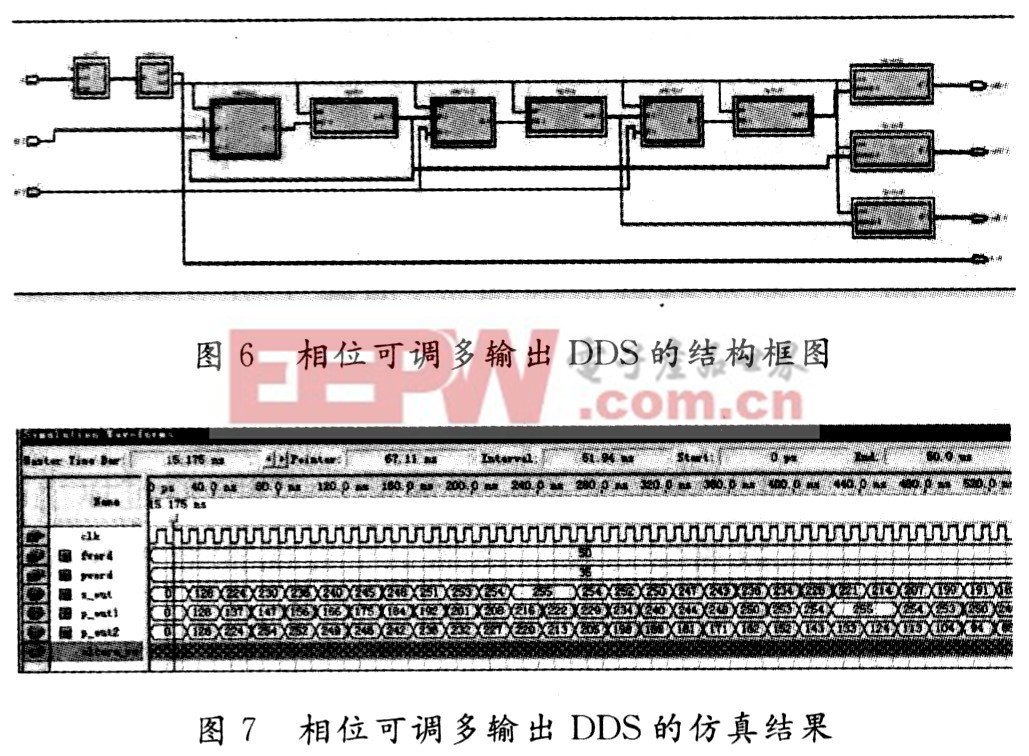

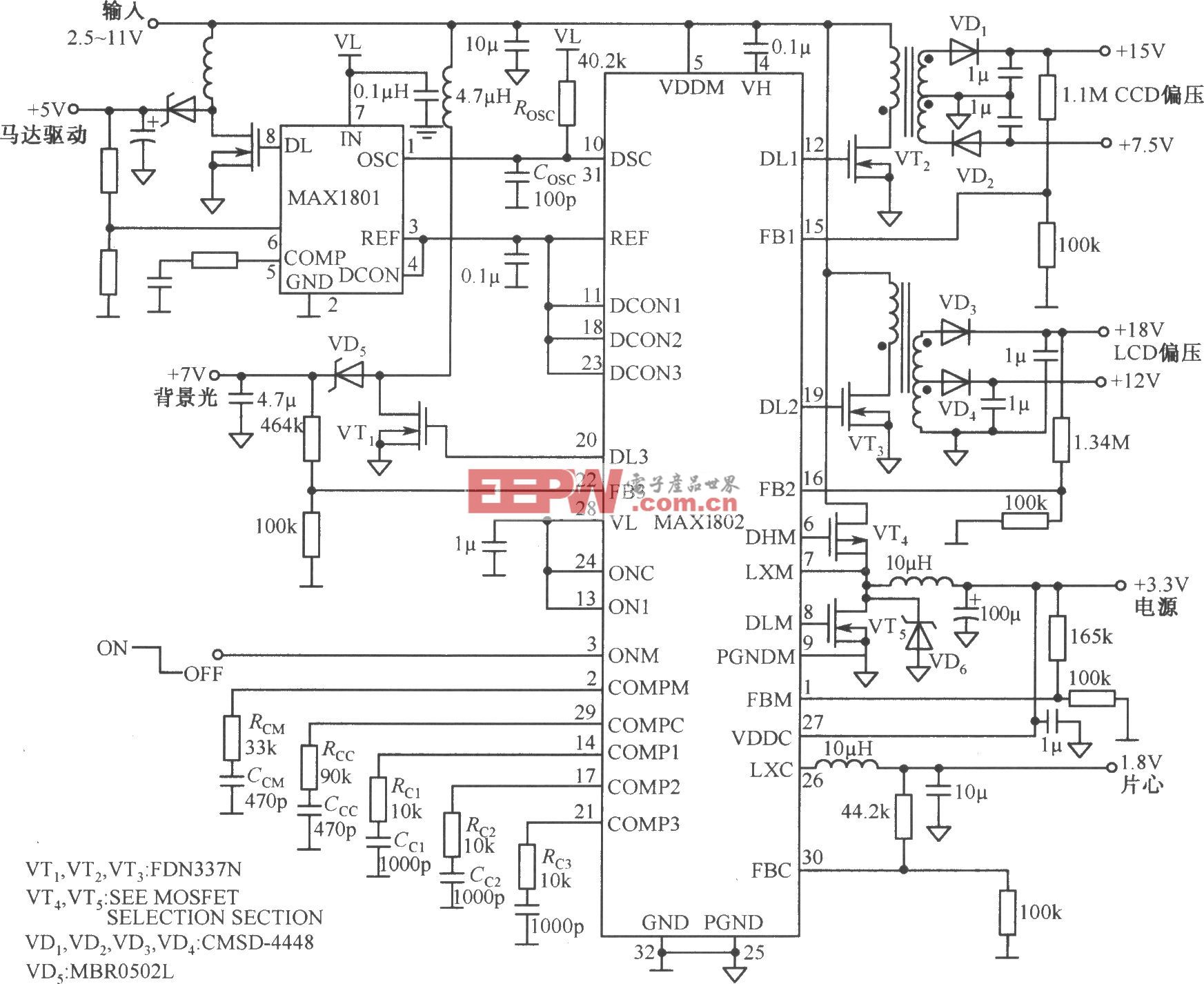

本設(shè)計在Quartus Ⅱ中進(jìn)行分析和綜合后,得到該相位可調(diào)多輸出DDS的結(jié)構(gòu)如圖6所示。

在Quartus Ⅱ中,輸入控制信號:Fo=100 MHz,fword=50,pword=35,進(jìn)行仿真,其仿真結(jié)果如圖7所示。在Quartus中生成的仿真數(shù)據(jù)經(jīng)過驗證完全正確,得到了同頻和可調(diào)相的三個正弦波的幅值數(shù)據(jù)序列,完全滿足設(shè)計要求。

4 結(jié) 語

本設(shè)計運用VHDL硬件編程語言和DDS技術(shù),結(jié)合FPGA高速器件,實現(xiàn)了多路信號的同步輸出,很好地解決了要求信號之間同頻率可調(diào),相位連續(xù)可調(diào)的問題,且具有易于程控、相位連續(xù)、輸出頻率穩(wěn)定度高、分辨率高等優(yōu)點,并且采用一個FPGA塊就解決了傳統(tǒng)上需要三個DDS才能解決的問題,也大大降低了設(shè)計成本。

評論