一種基于FPGA高性能H.264變換量化結構設計

摘 要:H.264作為最新的視頻編碼標準具有很高的壓縮性能,對它的研究具有重要的意義。根據H.264的變換量化算法設計一種基于FPGA的高性能變換量化處理結構,該結構采用流水線操作和分時復用技術。結果顯示,該設計既節省了資源,又保證了效率;能夠同時處理整個4× 4塊的全部16個殘差輸入數據,并在236個時鐘內完成對1個宏塊的殘差數據從輸入到反變換輸出重建值的完整變換量化過程。它的處理速度和性能大大提高,可用于硬件加速。

關鍵詞:H.264;變換;量化;FPGA

0 引 言

H.264高效的編碼效率是以其高復雜性為代價的,因此制約了它在高分辨率、實時處理等方面的應用。而FPGA器件采用流水控制策略和并行處理方式,可為H.264復雜的編碼模塊提供硬件加速引擎。變換量化模塊在H.264編碼算法中被頻繁調用。因此研究在盡量合理控制其資源消耗的前提下,提高變換量化模塊的工作頻率及處理數據的吞吐量,并完成變換量化一系列完整功能的變換量化結構具有重要的實際意義,也成為當前研究的首要問題。H.264.變換是基于DCT的,其全部采用整數DCT變換,這樣就避免了正變換和反變換的失配問題,既不丟失解碼精度,也適合于FPGA硬件實現。

1 算法原理及分析

1.1 變換算法及分析

H.264變換是整數DCT變換,該算法實現了編碼端和解碼端反變換之間的零匹配,從而減少了解碼精度的丟失。通常H.264變換編碼以4×4塊為單位,核心變換矩陣如下:

當核心變換矩陣中a=1時,為DCT正向變換矩陣Cf,;若將DCT正向變換矩陣Cf,中所有的2變為1,并保持所有符號不變,則變成Hadamard變換矩陣Hi;若將以上矩陣中所有的2變為1,并使a=1/2,保持所有符號不變,則為DCT反向變換矩陣CTi。

1.2 量化算法及分析

H.264的分級標量量化器支持多達52個量化步長Qstep,用量化參數QP進行索引。范圍廣闊的量化步長能夠靈活準確地控制比特速率和質量之間的平衡。

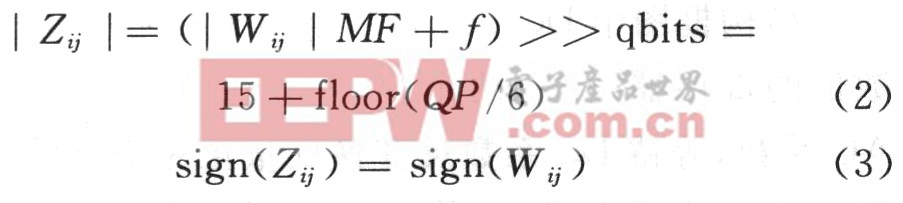

在整數算法中,量化過程可以用以下運算來實現:

式中:W為殘差系數;>>表示二進制右移;幀內塊和幀間塊f分別為2qbits/3,2qbits/6;MF為乘法因子,其值可根據W(i,j)在矩陣中不同的位置和量化參數QP的不同,查乘法因子表得到。

系數z的反量化方式如下:

![]()

式中:尺度因子V可根據Z(i,j)在矩陣中不同的位置和量化參數QP的不同,查尺度因子表得到。

2 FPGA硬件設計及實現

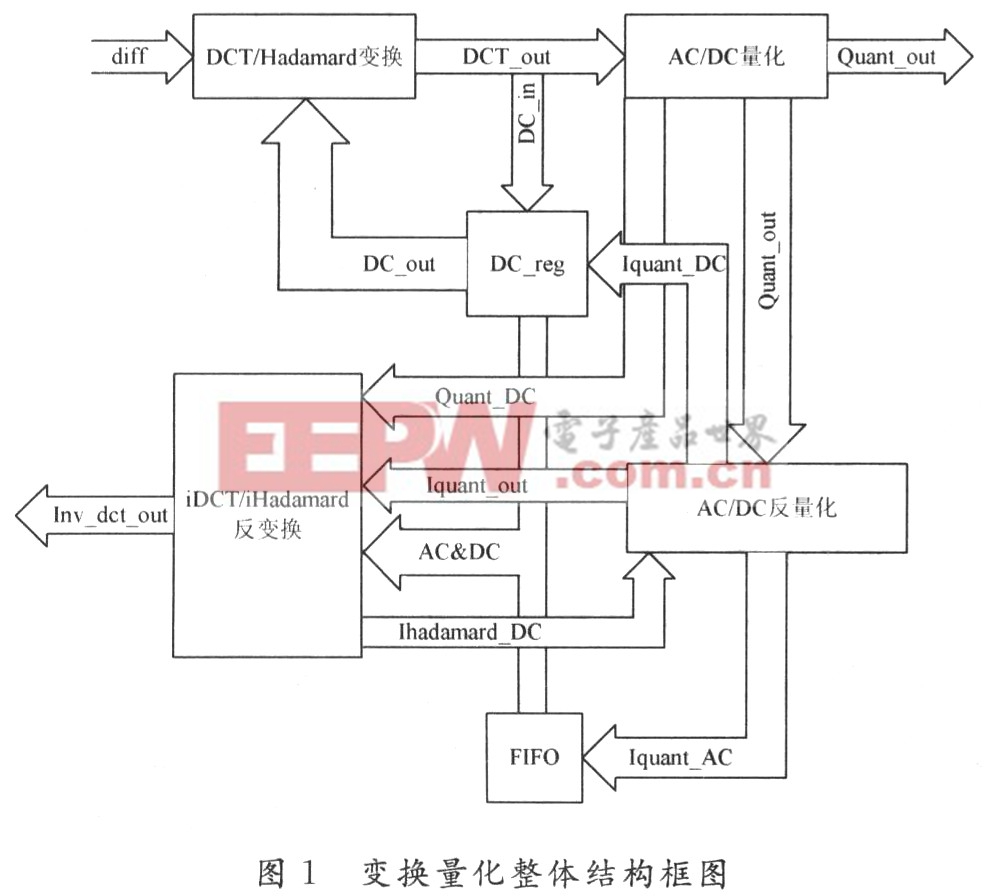

2.1 變換量化硬件整體結構

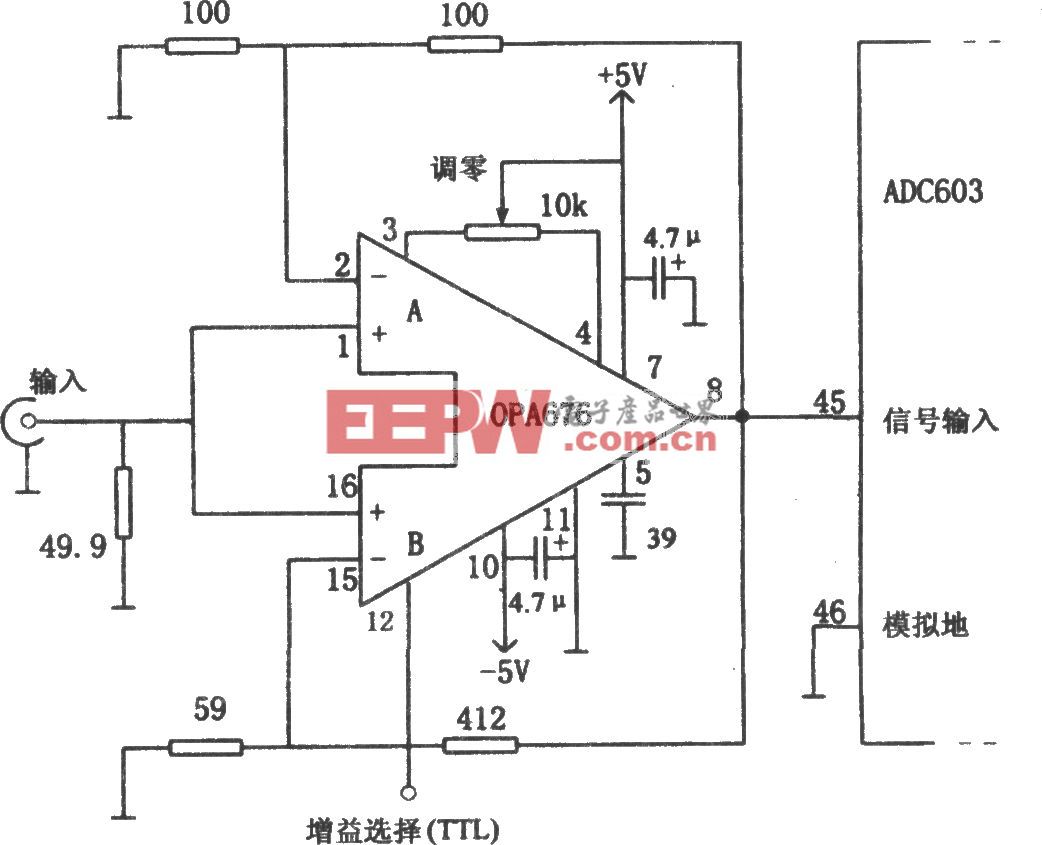

在H.264編碼器中經過預測后得到的殘差數據經過變換T、量化Q后的數據分為兩路:一路經過重排序Recoder后用于熵編碼;另一路為重建通路,經過反量化Q-1、反變換T-1后與預測值P相加得到重建值,用于后面的宏塊的預測編碼。

H.264編碼標準中,在幀內預測方式下,首先對16×16宏塊(亮度分量)的16個4×4塊進行DCT變換,然后提取出DC系數組成一個4×4 DC塊;對于這個4×4 Dc塊要先進行Hadamard變換,然后量化。在重建通路中需要注意:對于4×4 DC塊,要先進行反Hadamard變換,再進行反量化,目的是使反變換的動態范圍最大;再依據這個4×4 DC塊中16個數值對反量化后的16×16宏塊進行反DCT變換。對于色度分量的DC系數也是一樣需要經過進一步變換。H.264變換量化整體結構主要分為4大模塊,其框圖如圖1所示。

結構框圖中DC_reg是一組用于存儲所有的DC系數值的寄存器,使用兩個同步FIFO存儲反量化后的AC系數,等待DC系數反變換反量化完畢以后,再一起送人最后的反DCT變換模塊中進行處理。兩個同步FIFO在時鐘控制下先后進行寫操作,其中一個存儲4×4塊反量化輸出的其中兩行數據,另一個在下一時鐘存儲這個4×4塊反量化輸出的另兩行數據。讀取時,則同時對兩個FIFO進行讀操作,即一個時鐘內這個4×4塊的反量化后的全部16個數值同時出現在反變換模塊的輸入端。

評論