在FPGA中實現源同步LVDS接收正確字對齊

在串行數據傳輸中,數據接收端需要一些特定的信息來恢復出正確的字邊界,以確定串行碼流中哪些比特屬于原始并行數據里的同一時鐘節拍里的數據,這一處理過程稱為字對齊(Word Aligner)。一些標準的協議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種方案都可以進行正確處理。那么,如何FPGA中利用低頻源同步時鐘實現低壓差分信號(LVDS)接收字對齊呢?

本文引用地址:http://www.104case.com/article/191976.htm

在串行數據傳輸中,數據接收端需要一些特定的信息來恢復出正確的字邊界,以確定串行碼流中哪些比特屬于原始并行數據里的同一時鐘節拍里的數據,這一處理過程稱為字對齊(Word Aligner)。一些標準的協議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種方案都可以進行正確處理。對于標準協議,FPGA通常都會有知識產權(IP)模塊提供。本文主要討論在FPGA中利用低頻源同步時鐘實現低壓差分信號(LVDS)接收字對齊的設計方法及步驟。

LVDS已經成為業界高速傳輸最普遍應用的差分標準。LVDS的優勢包括:由于采用差分信號帶來的對共模噪聲的免疫能力,進而提高了抗噪聲能力;功率消耗較小,噪聲較小等。由于LVDS有比較好的抗躁聲特性,它可以采用低至幾百毫伏的信號擺幅,進而可以支持更高的數據速率。

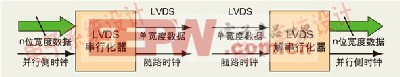

LVDS串行器/解串器(SERDES)可以完成多位寬度的并行信號到LVDS串行信號的轉換以及反方向操作,如圖1所示。有些器件提供圖1中的隨路時鐘,但有些器件可能并不提供,這時LVDS解串器還必須具有時鐘恢復(CDR)功能。市面上有各種規格的LVDS SERDES器件,此外FPGA或其它一些器件也都能集成LVDS SERDES模塊。

圖1:LVDS串行器/解串器的功能示意圖。

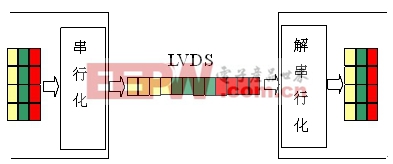

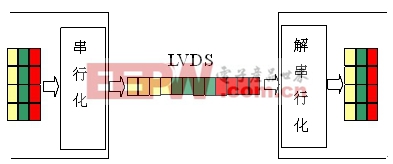

為確保正確的數據傳送,通過LVDS接收器后必須能恢復字順序,即輸入到LVDS串行器的最高比特能夠正確地出現在解串器恢復輸出數據的最高比特位置上,至少是需要預先知道出現在哪個比特位置上后再進行調整。圖2和圖3分別給出了4位寬度下字順序得到保留和沒有得到保留的例子。對于圖3的情況,需要采用一種方法找把字順序調整過來。

圖2:字順序得到保留。

圖3:字順序沒有得到保留。

字順序的調整通常采用尋找訓練碼來進行。一些標準的協議通常會定義特殊的碼型來進行字對齊處理,比如8B/10B編碼中K28.5碼型的主要功能就是字對齊處理。發送端在有效數據中插入K28.5碼型,接收端在收到的數據中尋K28.5碼型,找到之后以這個碼型為參考得到正確的并行數據輸出。此外,諸如SDH協議就利用幀頭位置的A1A2字節來進行字對齊處理。

另外一些相對低速的LVDS接口也利用低頻的源同步時鐘來攜帶字對齊信息,以便在接收端實現正確的數據恢復。這里的低頻源同步時鐘也如圖1中的隨路時鐘,LVDS數據和隨路時鐘之間的倍數關系通常等于LVDS串行化時的倍數因子。比如,德州儀器(TI)的SN65LVDS95 LVDS發送器,不僅可完成21:3的LVDS串行化發送,還將21位的并行數據和時鐘串行化成3路LVDS數據輸出和1路時鐘輸出。串行化因子的值等于7,所以輸出時鐘的頻率是LVDS數據速率的七分之一。通過這個隨路時鐘,配套的解串器SN65LVDS96就能夠正確恢復并行數據。

與這類單獨的LVDS SERDES器件相比,FPGA集成LVDS模塊能提供更高的集成度,并簡化硬件設計、節省PCB面積,從而降低應用成本。高端FPGA還在I/O單元里固化了LVDS串行器/解串器,支持非常高的速率,比如Altera公司的Stratix III系列。

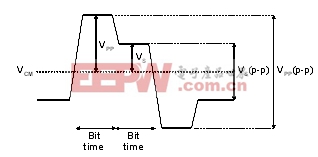

Stratix III FPGA系列是Altera公司基于TSMC 65nm工藝的高端FPGA,是業界高密度高性能可編程邏輯器件中,功耗最低的產品系列。Stratix III 器件可以同時提供最多276對LVDS串行化發送模塊和276對LVDS解串行化接收模塊,每路LVDS最高可以支持1.6Gbps。此外,它還獨家提供可編程的輸出擺幅和預加重功能,以支持長距離背板傳送,如圖4所示。

圖4:Stratix III 支持可編程的輸出擺幅(Vs(p-p))和預加重(Vpp(p-p))。

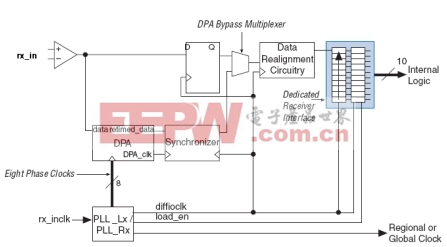

圖5顯示了Stratix III的LVDS接收器中固化在I/O單元里的模塊。源同步的低頻時鐘rx_inclk通過PLL倍頻移相后得到DIFFI/OCLK,對輸入數據rx_in進行采樣,采樣后的數據可以進行最高因子為10的解串行化。

圖5:Stratix III I/O固化的LVDS接收器。

由于FPGA具有非常高的靈活性,比如支持不同LVDS輸入數據和輸入時鐘之間的倍頻關系,以及不同的解串行化因子,所以Stratix III LVDS硬核模塊的輸出字順序通常是不確定的,每次上電或者復位后字順序都有可能發生變化,使用時需要根據特殊碼型進行字對齊處理。

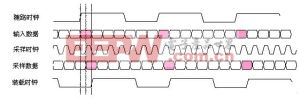

當輸入到FPGA的數據和時鐘之間的倍數關系等于解串器的解串行化因子時,FPGA與單獨的LVDS解串器一樣,有確定的字順序輸出,可以在沒有訓練碼型的情況下繼續正常應用。圖6是解串行化因子為7時的時序圖。假設隨路時鐘的上升沿對應數據的最高比特,在FPGA內部,PLL會從隨路時鐘產生一個進行過相位調整的7倍頻率采樣時鐘。此時鐘對輸入數據進行采樣后送入解串器,通過控制解串器的裝載時鐘相位,得到確定的并行數據輸出字順序。裝載時鐘的相位相對隨路時鐘相位的固定差異是通過接收PLL的相位控制來實現的,因此必須在輸入時鐘穩定后再釋放PLL的復位控制,或者等輸入時鐘穩定后再復位PLL一次,否則輸出的字順序在每次上電時都可能不固定。

圖6:LVDS接收及解串行化時序圖。

評論