FPGA在激光測距機電路檢測系統中的應用

3.1 SPI通信接口的實現

SPI接口是一個同步、全雙工串行接口,最大數據位速率為時鐘速率的1/8,只要遵循同一時刻只有一個主機和從機通信的原則,在同一條總線上可以有多個主機和從機。SPI口因接口簡潔擴展方便等優良特性,廣泛應用于串行存儲器(如DataFlash、3線 E 2PROM)、串行外設(如ADC、DAC、LCD控制器、CAN控制器)和外部協處理器中。

在第三方軟件 Altera SOPC Builder中可直接定制 SPI接口的 IP核,在本系統中采用 Verilog HDL來描述實現。 在設計中,MCU作為 SPI通信的主機,FPGA的SPI接口作為從機。SPI口有四種不同的數據傳輸格式的時序,這里通過設置 SPCR寄存器選擇CPOL=0、CPHA=0模式,以下是其實現代碼:

always @(posedge sck or posedge cs)

begin:chy本文引用地址:http://www.104case.com/article/191973.htm

integer i;

if(cs) begin data=0;i=0;miso=1”b’Z; end

else begin

if(sck)

begin

data= data1;

data= data+mosi;

miso=(send_data>>(7-i)) 8'h01;

i=i+1;

if(i==8) begin

rev_byte= data;

end end end end

3.2時鐘分頻的實現

Verilog HDL所描述的所有組合邏輯或時序邏輯電路的功能都是在各自輸入時鐘的節拍下工作的,而對于不同的功能模塊,因其電路精度要求不同對輸入時鐘的要求也不同,時鐘頻率越低,對 FPGA綜合、布局布線的要求也越低,所設計出的電路也越穩定。在本設計中,系統時鐘由外部 100MHz晶振提供,系統內部模塊要用到的時鐘有 100MHz、1MHz、 1KHz、10Hz和 1Hz五種,由計數器分頻實現,限于篇幅不詳述。

3.3命令解釋與決策的實現 FPGA要完成與 MCU的數據交換,又要指揮各測試模塊對指定通道信號的特定參量的測試,還要執行成百上千組時序信號激勵和開關量信號激勵,任務錯綜復雜,需要一個對命令的解釋和決策執行機制。在具體實現上,首先對 MCU的命令號進行區間劃分,決策模塊收到從 SPI接口模塊的命令后,判斷命令的類別,分別針對握手聯絡命令、復位命令、測試命令(包括通道號、測試指標、時鐘輸入的選擇)、激勵發生命令(包括通道號、時序信息)、發送測試結果命令(通過 SPI接口將測試結果發送給MCU)等去觸發相應 FPGA內部模塊動作。

3.4信號測試的實現

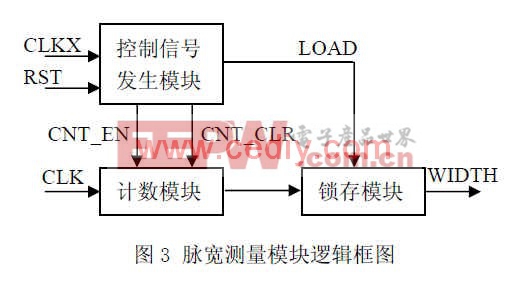

信號測試功能包括對輸入信號的脈寬測試、周期測試、特殊類型信號的測試等內容,限于篇幅,下面對比較典型的脈寬測試進行闡述。例如對于負脈沖信號,測試其脈寬即是測量其在某時段低電平的維持時間,可以通過計算時標信號的個數來實現。設時標信號周期為Ts,時標個數為N,則脈寬為W=Ts*N,其主要部分是計數功能,并將得到的數予以鎖存。計數模塊與鎖存模塊由控制信號發生模塊控制,其邏輯框圖如圖 3所示。

其中 CLKX為被測脈沖,CLK為時標信號,RST為系統復位信號,WIDTH為脈寬計算結果。圖中有三個控制信號:計數允許信號CNT_EN、計數清零信號 CNT_CLR和鎖存信號LOAD,分別控制計數模塊和鎖存模塊。

在實際測試中發現,由于外界干擾的影響,在被測信號出現正常脈沖前會出現多個窄帶

干擾脈沖,這個脈沖的短暫低電平會讓計數模塊產生誤動作,從而得出錯誤的計算結果。本文采取前級窄帶脈沖過濾的方法,有效地消除了外界的干擾。其具體做法是外加一個計數模塊判斷輸入信號的低電平時間是否超過一定門限,超過則觸發其后的控制信號發生模塊動作,否則不觸發。 值得注意的是在后面的計數模塊里要加上前級的門限值。

3.5激勵信號的實現

檢測系統所要產生的激勵信號包括時序信號和開關量信號,時序信號的產生相對復雜,其實現機理如圖 4所示。其中,START是啟動信號,控制時序產生模塊的啟動與停止;EX_SYNC是外同步信號,在某些場合下,時序信號的產生需要與外界信號的同步,此信號用于控制信號發生的時基;計數模塊負責在 CNT_EN和 CNT_CLR等控制信號下計數,實時觸發相應的時序序列輸出;LOCK信號用于鎖定末態時序序列的狀態。

評論