基于FPGA的串行接收模塊的設計

1 前言

隨著FPGA的飛速發展與其在現代電子設計中的廣泛應用,越來越多的實驗和設計中會運用FPGA與RS232通信。與此同時, FPGA具有功能強大、開發過程投資小、周期短、可反復編程等特點。筆者在FPGA芯片上集成了串行接收功能模塊,從而簡化了電路、縮小了電路板的體積、提高了可靠性。本文主要介紹圍繞FPGA所設計的符合 RS232標準的串行接收模塊。

2 異步串行通信原理

串行通信分為兩種類型:同步通信方式和異步通信方式。本設計采用的是異步通信方式,其的特點是:通信的發送方和接收方各自有獨立的時鐘,傳輸的速率由雙方約定。國際上規定的一個串行通信波特率標準系列是:110、300、600、1200、1800、2400、4800、9600、 19200,單位是 bps。本文采用的是 19200bps。

異步傳輸是一個字符接一個字符傳輸。一個字符的信息由起始位、數據位、奇偶校驗位和停止位組成。每一個字符的傳送靠起始位來同步,字符的前面是一位起始位,用下降沿通知接收方傳輸開始,緊跟著起始位之后的是數據位,傳輸時低位在前、高位在后,字符本身由5~8位數據位組成。數據位后面是奇偶校驗位,昀后是停止位,停止位是高電平,標志一個字符的結束,并為下一個字符的開始傳送做準備。停止位后面是不定長度的空閑位。停止位和空閑位都規定高電平,這樣可以保證起始位開始處有一個下降沿,如圖1所示。 3 硬件接口電路原理設計

在串行通信中,普遍采用的是 RS232-C接口的標準。 RS232-C接口信號引腳的連接方式規定了25芯的D型連接器DB-25,本設計采用的是一個 9芯的D型連接器DB-9,并且用昀為簡單常用的三線制接法,即地、接受數據和發送數據三腳相連。

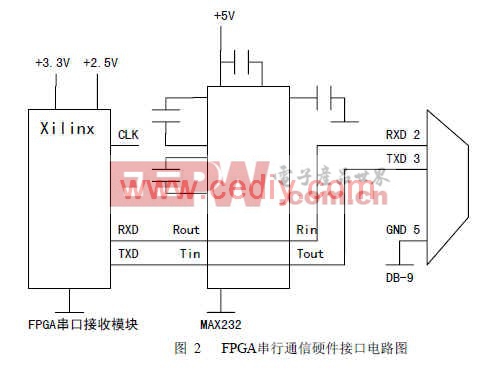

本設計的硬件接口電路圖如圖2所示,由三部分組成: FPGA串口接收模塊、 MAX232和DB-9。FPGA采用的是Xilinx公司的SPARTAN系列的 XC2S50芯片,其封裝為TQ144。 MAXIM公司的MAX232CPE是為滿足EIA/TEA-232E的標準而設計的,具有功耗低、波特率高、價格低等優點。工作電源為 +5V,外界電容僅為 luF,為雙組 RS-232收發器。MAX232有兩個發送器,本設計只用其中一個發送器,另外一個發送器的輸入端接地、輸出端懸空。

異步數據接收過程可作為一個整體來實現,數據由 DB-9的RxD端輸入,經過 MAX232進行電平轉換由FPGA串口接收模塊的 RxD端進入,然后在串口接收模塊內部對接收來得數據進行判斷,并昀終實現對FPGA輸出信號的控制。

評論