分布式運(yùn)算單元的原理及其實現(xiàn)方法

若將式(4)每個方括號之間的加法并行執(zhí)行,即將每個DA查找表的輸出采用并行的加法,就得到了全并行結(jié)構(gòu)。現(xiàn)將式(4)中的某個方括號重寫如下,并縮寫為sum:本文引用地址:http://www.104case.com/article/191941.htm

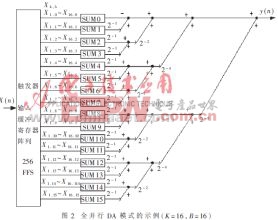

利用式(6),可以得到一種直觀的樹形陣列,如圖2所示。

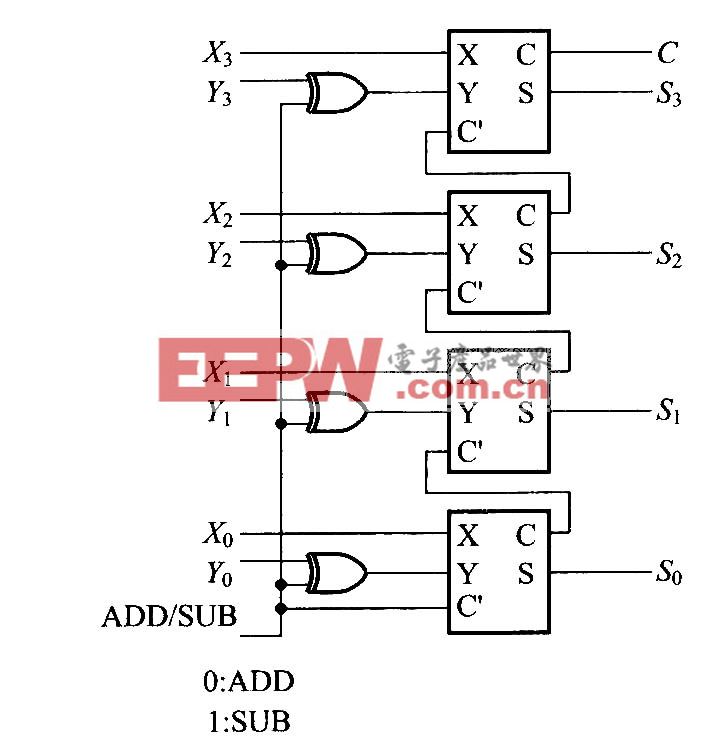

圖2中,首先要建立一個K×B位的寄存器陣列,將其輸出進(jìn)行排列,用所有K個輸入數(shù)據(jù)的相同位,對 DA查找表尋址,從圖中可以看出,當(dāng)B=16時,輸入到輸出所需的路徑最長,該路徑為關(guān)鍵路徑,影響著電路處理的速度,在進(jìn)行設(shè)計時應(yīng)該注意到這點,所以應(yīng)該采用流水線設(shè)計方法[1],并進(jìn)行適當(dāng)?shù)募s束,其數(shù)據(jù)率可以達(dá)到50MHz。圖中的15個節(jié)點代表著15個并行的加法器,中間過程的數(shù)據(jù)寬度既可以保持雙精度(B+C)位數(shù)據(jù)(C是常數(shù)Ak的寬度),也可以采用截尾的辦法得到單精度B位數(shù)據(jù),可根據(jù)系統(tǒng)所要求的精度確定。

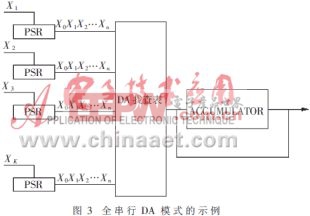

2.2 全串行實現(xiàn)方法

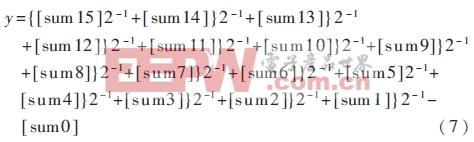

當(dāng)系統(tǒng)對速度的要求不是很高的時候,可以用全串行設(shè)計方法,即一個DA查找表,一個并行的加法器以及簡單少量的寄存器就可達(dá)到目的,這樣能夠節(jié)省大量的FPGA資源。同樣,設(shè)K=16,B=16,將式(4)改寫如下形式:

為了實現(xiàn)式(7),先從最低位開始,用所有K個輸入變量的最底位對DA查找表進(jìn)行尋址,得到了[sum15],將[sum15]右移一位即將 [sum15]乘2-1后,放到寄存器中,設(shè)為[tem15];同時,K個輸入變量的次低位已經(jīng)開始對DA查找表尋址得到[sum14],右移一位后,與 [tem15]相加,重復(fù)這樣的過程,直至得到[sum0],并用前面得到的累加結(jié)果減去[sum0]。要實現(xiàn)上述過程,需要K個長度為B的串并行轉(zhuǎn)換移位寄存器、一個容量為2K×C的DA查找表和一個累加器。該全串行電路的數(shù)據(jù)率為輸入數(shù)據(jù)抽樣頻率的1/B,即完成一次運(yùn)算需要B個時鐘周期。由此可以得到全串行DA模式,如圖3所示。

2.3 串并行相結(jié)合實現(xiàn)方法

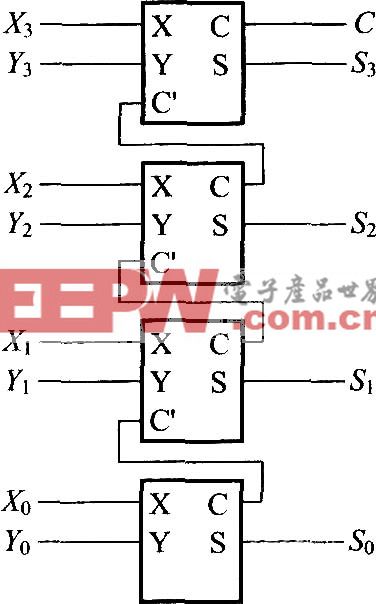

以上介紹的全串行方式是每個時鐘周期對所有K個變量的一位進(jìn)行串行處理,全并行方式是每個時鐘周期對所有K個變量的所有B位進(jìn)行并行處理;這兩種方法是針對速度優(yōu)化和資源優(yōu)化設(shè)計的兩種極限情況。在有些情況下,我們可以對這兩種情況進(jìn)行折中考慮,獲得最佳資源利用和系統(tǒng)速度。我們可以從每個時鐘周期對K個變量的兩位進(jìn)行處理開始著手,回顧一下式(5),并將該式改寫如下:

完成該式功能的功能框圖如圖4a所示。

評論