震驚!FPGA運算單元可支持高算力浮點

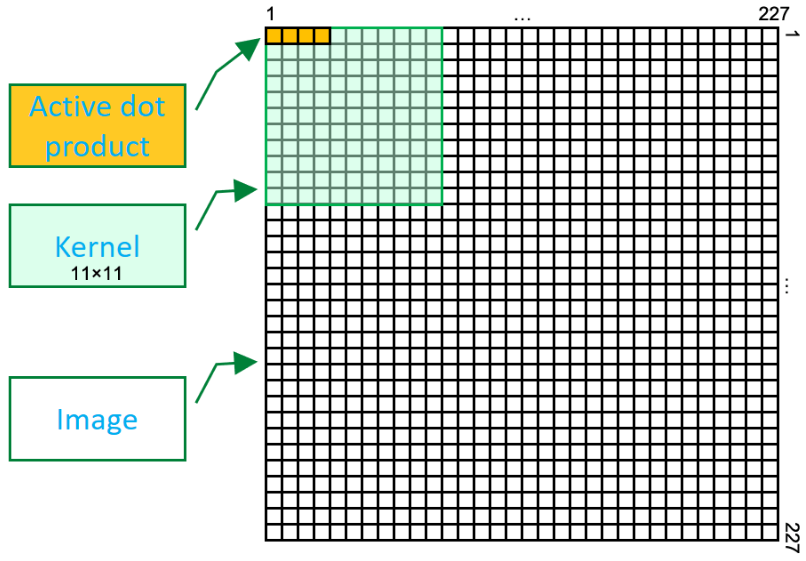

隨著機器學習(Machine Learning)領域越來越多地使用現場可編程門陣列(FPGA)來進行推理(inference)加速,而傳統FPGA只支持定點運算的瓶頸越發凸顯。 Achronix為了解決這一大困境,創新地設計了機器學習處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數格式進行拆分。

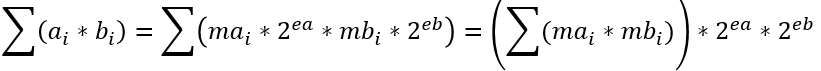

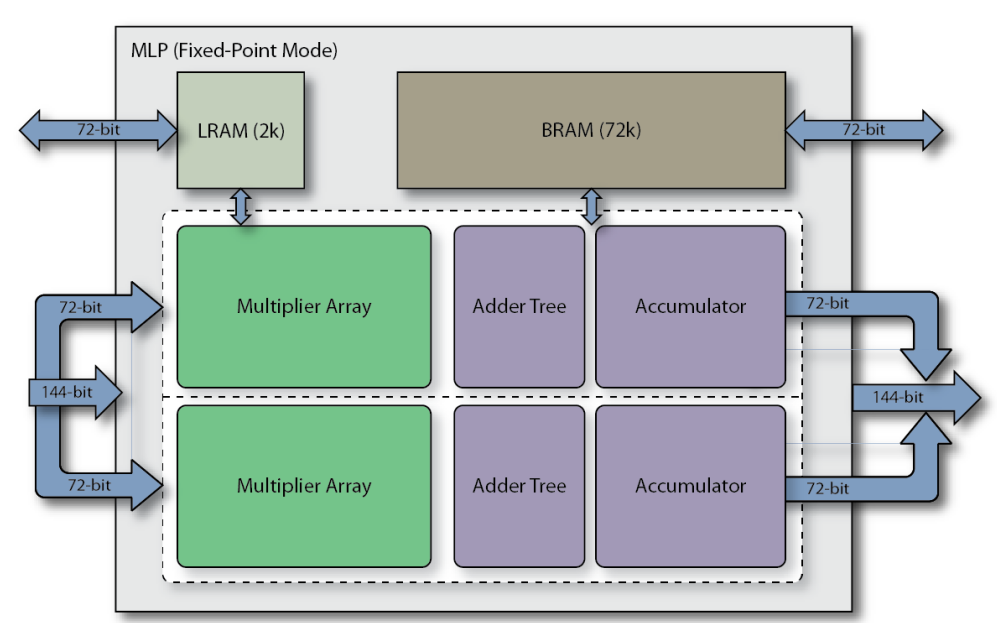

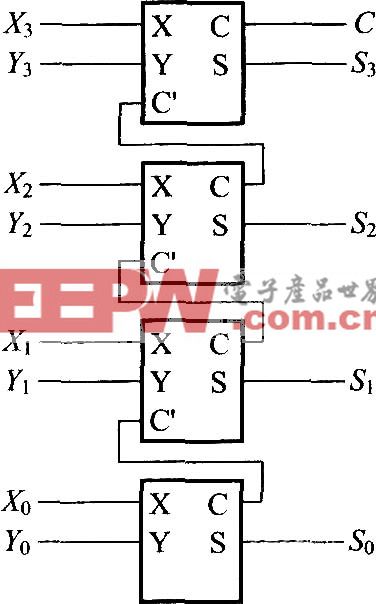

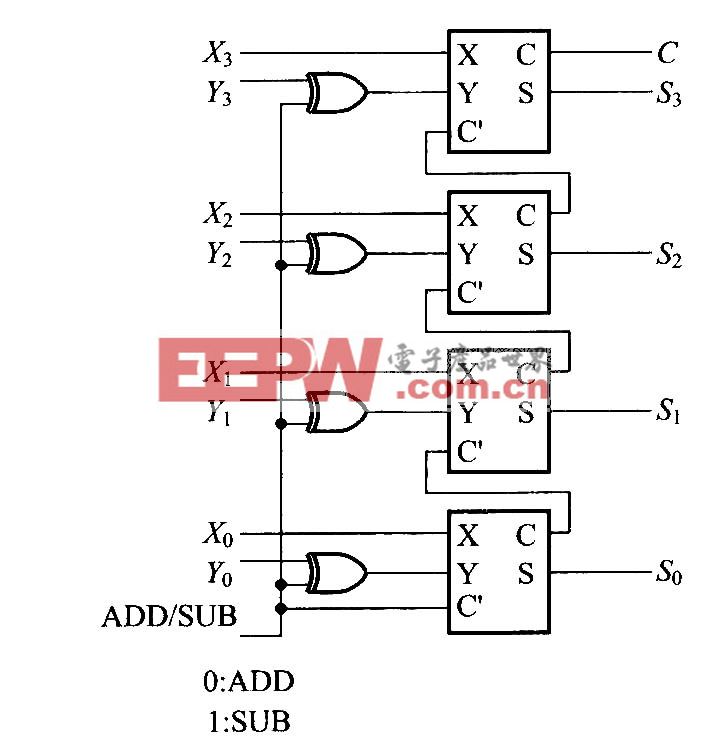

本文引用地址:http://www.104case.com/article/202003/410540.htmMLP全稱Machine Learning Processing單元,是由一組至多32個乘法器的陣列,以及一個加法樹、累加器、還有四舍五入rounding/飽和saturation/歸一化normalize功能塊。同時還包括2個緩存,分別是一個BRAM72k和LRAM2k,用于獨立或結合乘法器使用。MLP支持定點模式和浮點模式,對應下面圖1和圖2。

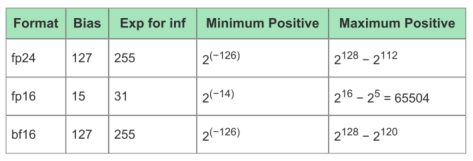

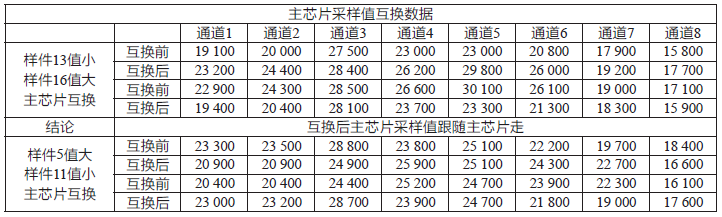

考慮到運算能耗和準確度的折衷,目前機器學習引擎中最常使用的運算格式是FP16和INT8,而Tensor Flow支持的BF16則是通過降低精度,來獲得更大數值空間。下面的表1是MLP支持的最大位寬的浮點格式,表2說明了各自的取值范圍。

而且這似乎也成為未來的一種趨勢。目前已經有不少研究表明,更小位寬的浮點或整型可以在保證正確率的同時,還可以減少大量的計算量。因此,為了順應這一潮流,MLP還支持將大位寬乘法單元拆分成多個小位寬乘法,包括整數和浮點數。詳見下表3。

值得注意的是,這里的bfloat16即Brain Float格式,而block float為塊浮點算法,即當應用Block Float16及更低位寬塊浮點格式時,指數位寬不變,小數位縮減到了16bit以內,因此浮點加法位寬變小,并且不需要使用浮點乘法單元,而是整數乘法和加法樹即可,MLP的架構可以使這些格式下的算力倍增。

表3是Speedster7t系列1500器件所支持的典型格式下的算力對比,可以看到,單片FPGA的浮點算力最高可達到123TOPS。

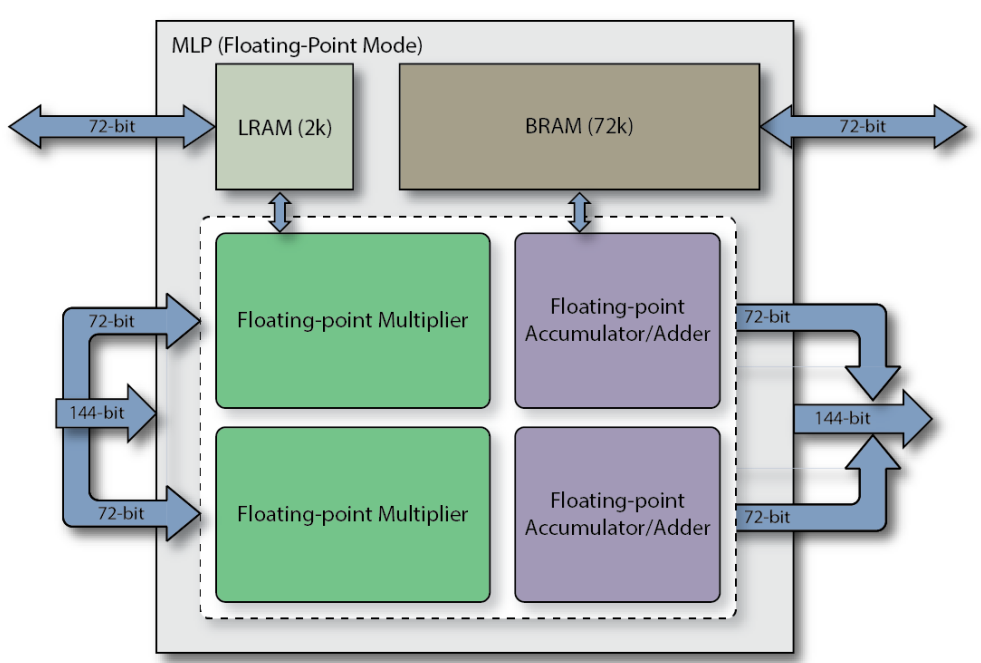

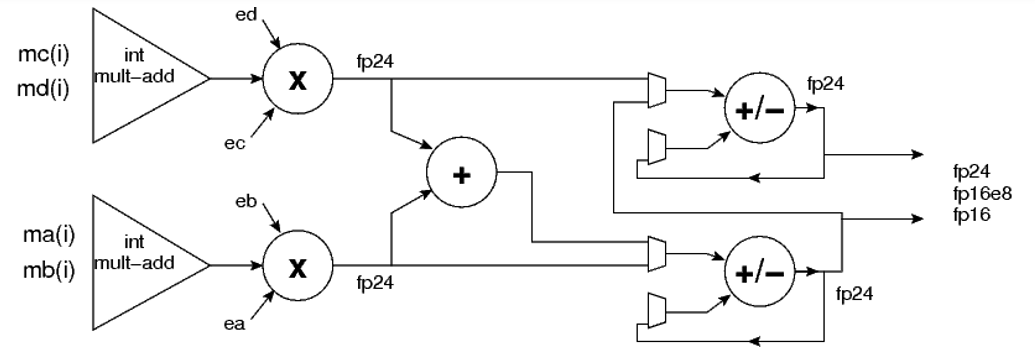

下圖3是MLP中FP24/FP16乘加單元的簡化結構圖,即一個MLP支持FP24/FP16的A*B+C*D,或者A*B,C*D。

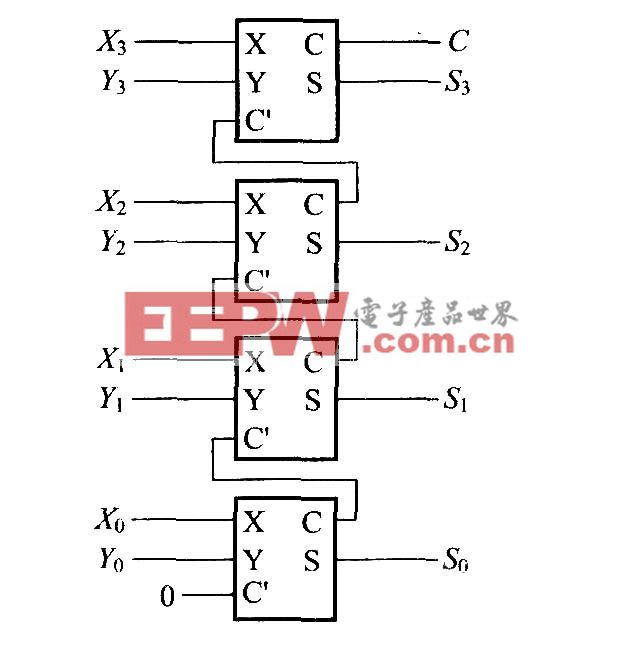

而以下的圖4則是塊浮點乘加單元結構。

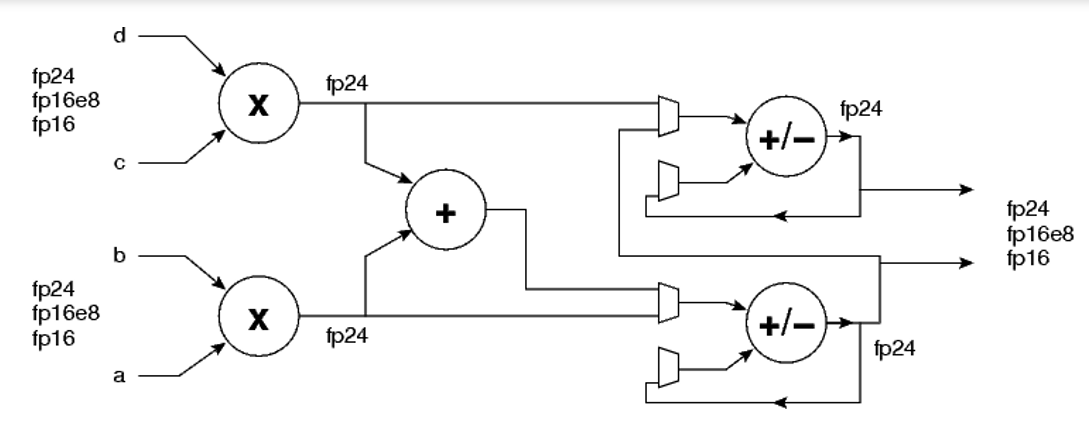

這里考慮浮點數序列塊,浮點數序列塊,各序列塊內均擁有相同的指數ea和eb。則(如下圖)

不難看出,乘法單元的個數取決于尾數(即整數)位寬。

圖1 定點模式下的MLP框圖

圖2 浮點模式下的MLP框圖

圖3 MLP中FP24/FP16乘加單元的簡化結構圖

圖 4 塊浮點乘加單元結構

| Format | FP Size | FP Exponent Size | Precision | MLP Name | Alternative Names |

| fp24 | 24 | 8 | 16 | FP24 | |

| fp16 | 16 | 5 | 11 | FP16 | binary 16,half precision |

| bf16 | 16 | 8 | 8 | BFLOAT16 | bfloat 15.(brain float) Not to be confused with block floating point. |

表1 MLP支持的最大位寬的浮點格式

| Format | Bias | Exp for inf | Minimum Positive | Maximum Positive |

| fp24 | 127 | 255 | 2(-126) | 2128 - 2112 |

| fp16 | 15 | 31 | 2(-14) | 216 - 25=65504 |

| bf16 | 127 | 255 | 2(-126) | 2128 - 2120 |

表2 不同運算格式的取值范圍

| Data Type | Matissa Size | Exponent | Multipliers /MLP | MLP Perf. (GOPS) |

| int 3 | 3 | n/a | 32 | 12,2880 |

| int 4 | 4 | n/a | 32 | 12,2880 |

| int 6 | 6 | n/a | 16 | 6,1440 |

| int 8 | 8 | n/a | 16 | 6,1440 |

| int 16 | 16 | n/a | 4 | 1,5360 |

| bfloat 16 | 8+hidden bit | 8 | 2 | 7680 |

| fp 16 | 12+hidden bit | 5 | 2 | 7680 |

| block float 3 | 3 | up to 8 | 32 | 12,2880 |

| block float 4 | 4 | up to 8 | 32 | 12,2880 |

| block float 6 | 6 | up to 8 | 16 | 6,1440 |

| block float 8 | 8 | up to 8 | 16 | 6,1440 |

| block float 12 | 12 | up to 8 | 4 | 1,5360 |

| block float 16 | 16 | up to 8 | 4 | 1,5360 |

| fp 24(8e) | 15+hidden bit | 8 | 2 | 7680 |

表3 Achronix的Speedster7t系列1500器件支持的典型格式的算力對比

(四位數一個逗號是為了方便讀數字,四位數加一個小數點即使萬)

| int size | mult per block | mult per MLP | int format |

| 3、4 | 16 | 32 | signed magnitude |

| 6、7、8 | 8 | 16 | signed magnitude |

| 16 | 2 | 4 | 2's complement |

表4 MLP中乘法單元的個數與整數位寬的關系

如需了解更多產品細節,請訪問Achronix網站以獲取產品資料,謝謝閱讀!Achronix官網:www.achronix.com。

評論