基于CPLD的DDS正交信號源的設計

4 軟件設計

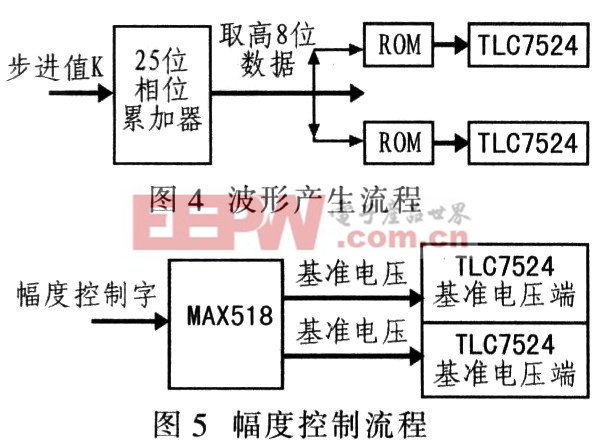

4.1 波形發生

在CPLD內設置25位相位累加器,高9位為ROM地址,低16 位為產生精確的讀ROM的點與點之間的時間間隔而設置的累加寄存器,即:單片機送一頻率控制字,由低16位寄存器每個時鐘都累加這個值,累加到低16位溢出,然后ROM的地址加1。ROM內的每個地址的數據表示當前波形的幅度,然后連續讀出數據并被平滑濾波后得出平滑、穩定的波形。波形產生流程如圖4所示。

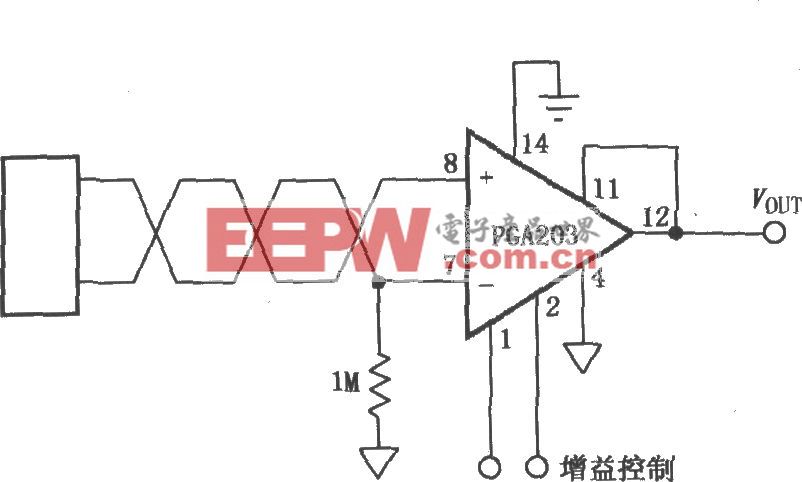

4.2 幅度控制

系統的幅度控制由MAX518完成,利用其內部電阻網絡實現數字電位器功能,輸出電壓作為TLC7524的基準電壓。圖5為幅度控制流程。

5 電路系統調試與參數測試

調試與測試所用儀器PC機、雙蹤模擬示波器YUAN-LONG、SS7200通用智能計數器、DT9205三位半數字萬用表。在戶1 kHz步進為20 mV下,測試電壓幅度。表1為電壓幅度測試,表2為輸出頻率測試。

6 結論

基于單片機和CPLD的DDS正交信號源,其頻率幅度可精密控制,擴展輸出頻率達300 kHz,增加掃頻輸出功能。采用紅外鍵盤控制頻率和幅度,采用液晶同步顯示信號的頻率和幅度;輸出端產生正弦波、方波、三角波、鋸齒波,梯形波、短形波、頻率突變的方波、尖脈沖數字信號等,且具有掃頻輸出的功能。測試結果表明,系統穩定可靠,人機交互界面友好,操作簡單方便。

評論