基于CPLD的DDS正交信號源的設計

1 引言

由于傳統的多波形函數信號發生器需采用大量分離元件才能實現,且設計復雜,這里提出一種基于CPLD的多波形函數信號發生器。它采用CPLD作為函數信號發生器的處理器,以單片機和CPLD為核心,輔以必要的模擬和數字電路,構成的基于DDS(直接數字頻率合成)技術、波形穩定、精度較高的多功能函數信號發生器。

2 系統設計

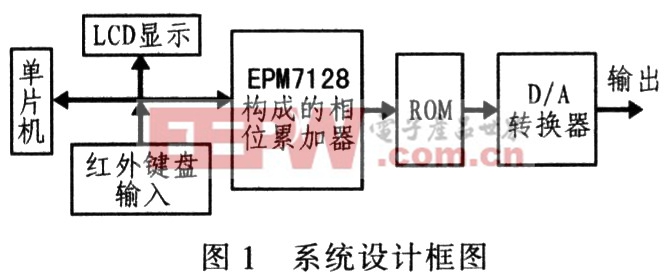

圖1給出系統設計框圖,該系統設計主要由CPLD電路、單片機電路、鍵盤輸入液晶顯示輸出電路以及D/A轉換電路和低通濾波器等電路組成。

2.1 頻率合成器

該系統設計采用直接數字式頻率合成DDS(Direct Digital Frequency Synthesis)技術,采用ROM存儲所需的量化數據,按照不同頻率求出頻率控制字。以K為步進對相位累加器進行累加,每累加一次,取出累加器的高8 位數據送至ROM,ROM根據不同的地址取出不同的數據送TLC7524進行轉換。再經過濾波即可得到所需要波形。由于DDS具有相對帶寬很寬,頻率轉換時間極短,頻率分辨率高等優點。此外,全數字化結構便于集成,輸出相位連續,頻率,相位和幅度均可實現程控。

評論