基于FPGA的示波器圖文顯示

2 系統硬件設計

2.1 總體控制模塊

基于本設計,系統控制模塊的部分是具有掩膜可編程門陣列的邏輯器件――FPGA。

Spartan系列FPGA是Xilinx公司可編程邏輯產品中的高性價比產品的代表,而Spartan-Ⅲ系列FPGA是為那些需要大容量、低價格電子應用的用戶而設計的。本系統使用的是XILINX公司的XC3S200型號芯片,其技術參數如下:

●4 320個邏輯單元;

●系統門密度200 k個;

●CLB陣列24*20,共480個;

●最大用戶I/O173,最大差分I/O76;

●分布式RAM容量30 Kbit,Block RAM容量216Kbit;

●嵌入式18x18乘法器支持高性能DSP應用;

●PCI和帶有LVDS的高速差分信號。

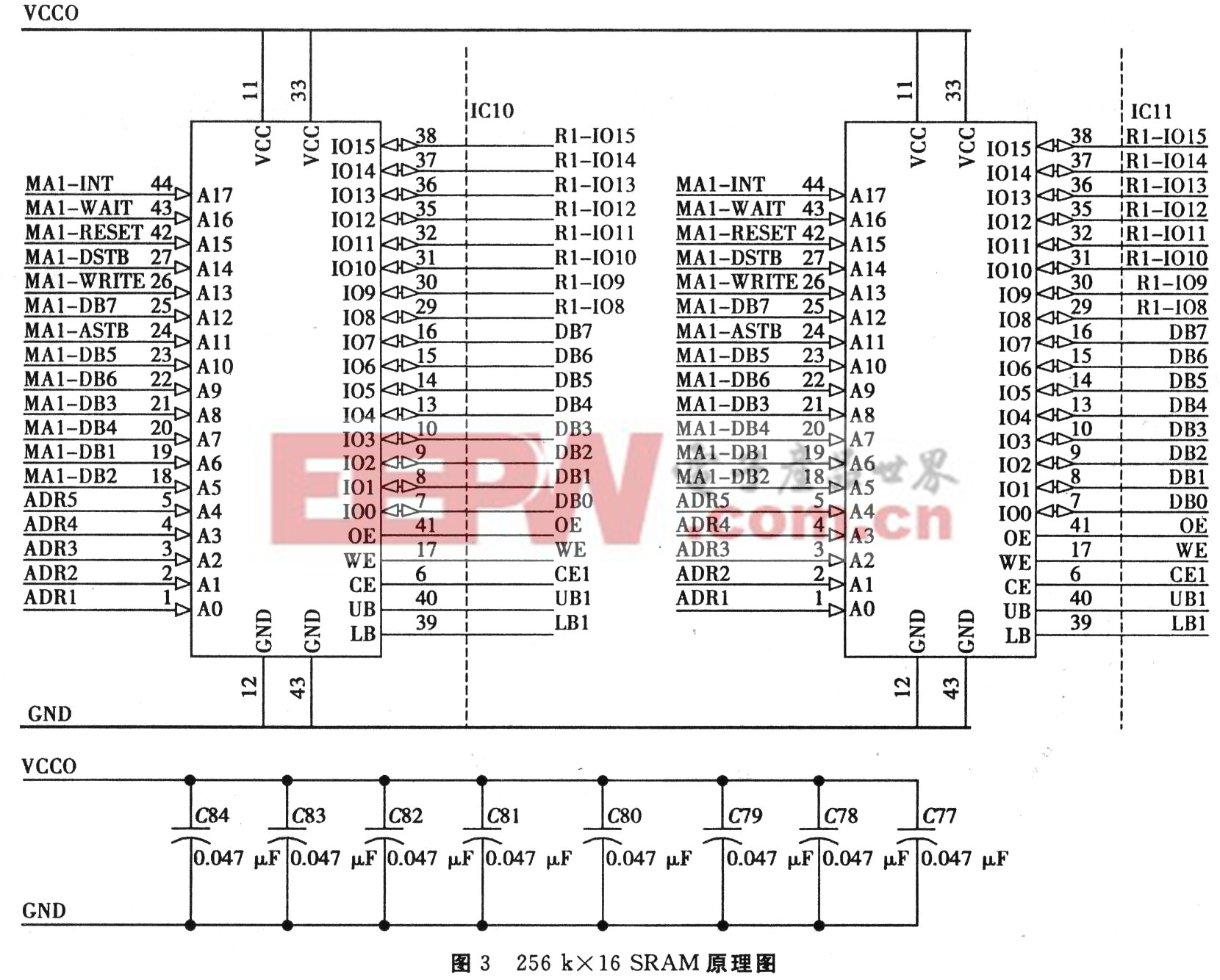

2.2 存儲單元模塊

由于FPGA基于CMOS SRAM工藝,不具備掉電保護功能,當無電源供電時,配置的數據丟失,芯片的功能也隨之丟失。因此,本設計采用FLASH存儲器在線重配置的方法。

2.3 外圍電路模塊

2.3.1 D/A轉換

在D/A選擇上,我們用的是美國半導體公司的 DAC0832,它具有8位并行、中速(建立時間1 us)、電流型、價格低廉等特點。它有單緩沖工作方式、雙緩沖工作方式兩種工作方式。單緩沖工作方式時,一個寄存器工作于直通狀態,一個工作于受控鎖存器狀態。在不要求多相D/A同時輸出時,可以采用單緩沖方式,此時只需一次寫操作,就開始轉換,可以提高D/A的數據吞吐量。雙緩沖工作方式時,兩個寄存器均工作于受控鎖存器狀態。當要求多個模擬量同時輸出時,可采用雙重緩沖方式。

它的技術參數為:建立時間1 us;8位并行;低功率損耗20 mW;支持電壓:5 V~15 V。

評論