基于對EPCS在線編程的FPGA可重構方法

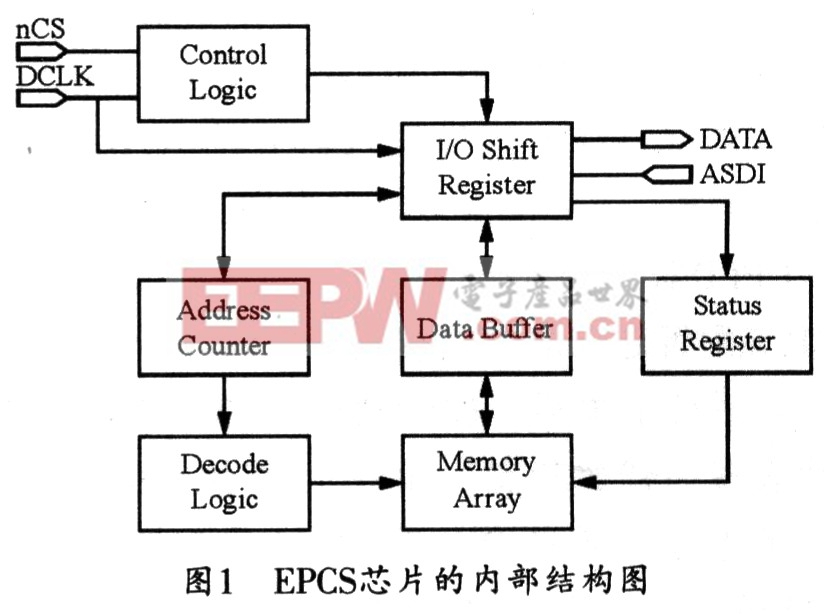

EPCS芯片的內部結構框圖如圖1所示,EPCS配置器件與所配置的FPGA器件的連接引腳有時鐘輸入管腳DCLK。可為串行數據的傳送提供時鐘,一般由FPGA發送;其次是串行數據輸出管腳DATA,用于向FPGA傳送配置數據;第三是主動串行數據輸入管腳ASDI,負責接收來自FPGA的不同字符串以實現對EPCS的讀寫控制;另外,還有片選信號nCS。本文引用地址:http://www.104case.com/article/191863.htm

上位機通過下載線用Quartus軟件工具對EPCS配置芯片進行配置程序的燒寫操作,其配置文件必須為pof文件格式。在所設計的系統文件編譯完成后,Quartus軟件就可以生成燒寫所需的pof格式文件。

2.3 可重構系統設計

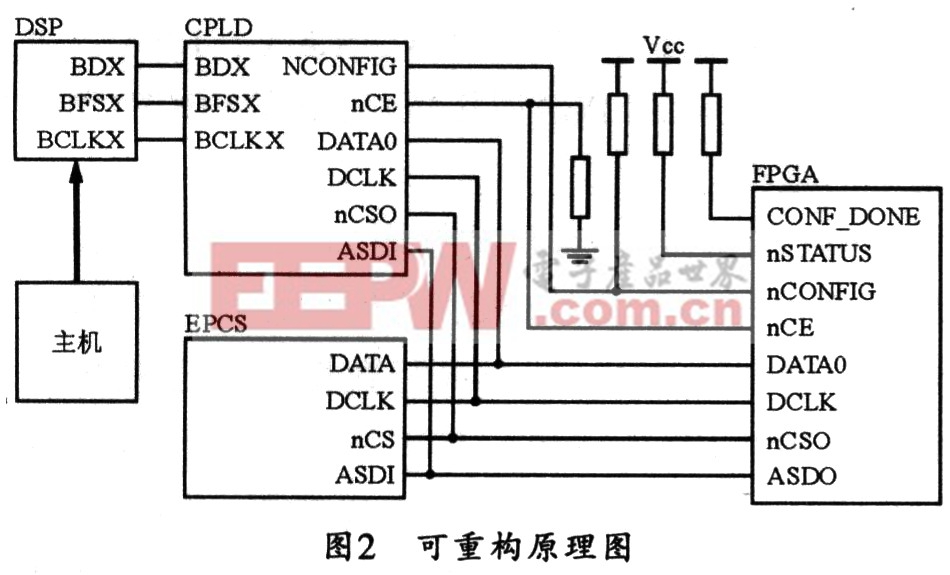

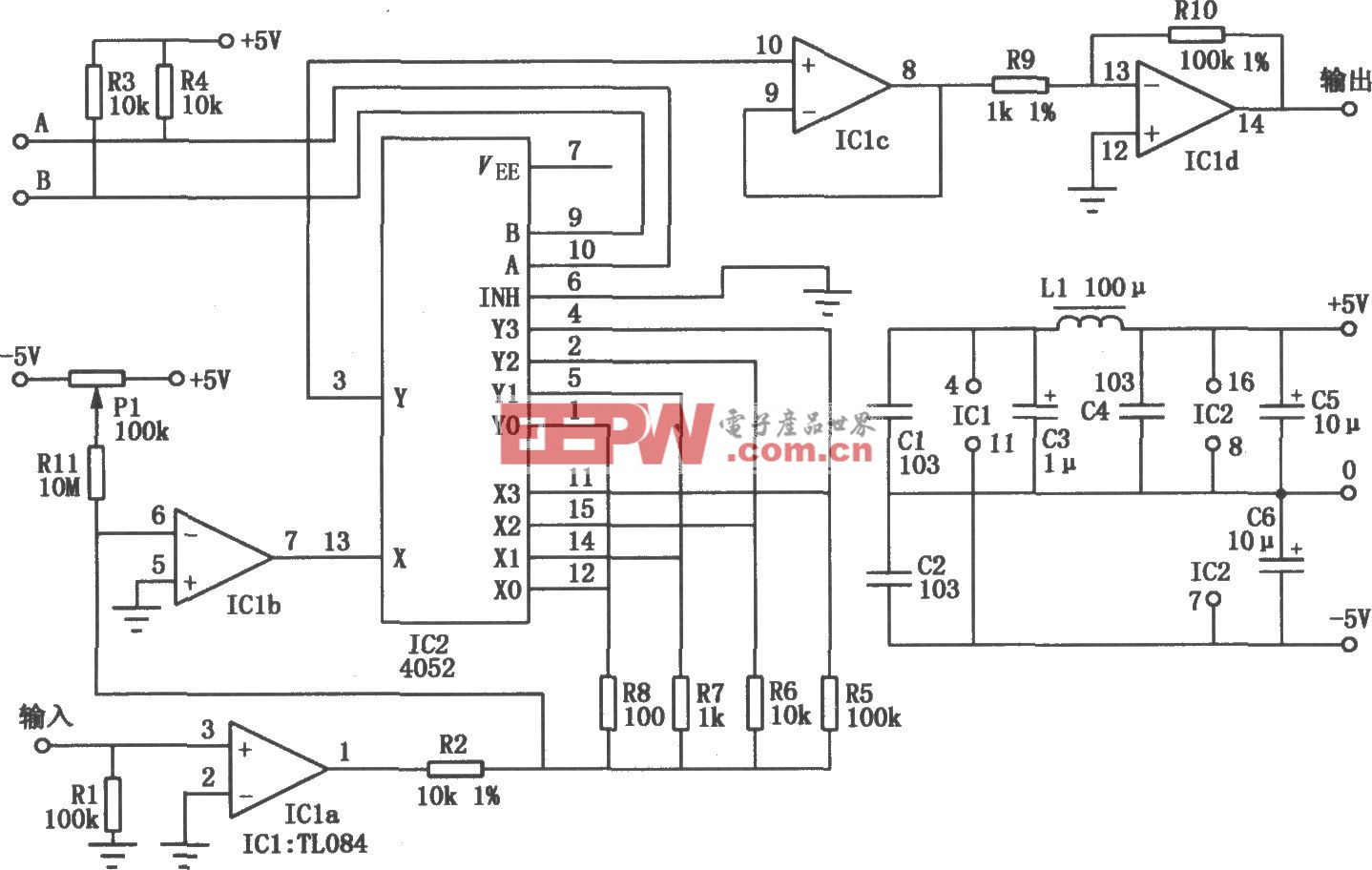

本設計主要是通過DSP的串口向CPLD器件發送控制命令以及要進行配置的數據包,CPLD解析命令后再執行相應的操作,以完成EPCS配置芯片所需的下載時序及配置數據。當EPCS配置芯片的數據下載完成后,再進行FPGA從配置芯片下載新的系統配置程序過程。一般情況下,在系統上電后,FPGA都要馬上從EPCS配置芯片中下載配置文件。在對EPCS配置芯片進行控制時,首先要讓FPGA釋放對EPCS配置芯片的控制,而且,在對EPCS配置芯片寫數據的操作完成后,又要將控制權交與FPGA,以便FPGA能夠下載最后一次完成的配置程序。本系統的可重構原理圖如圖2所示。

FPGA可重構系統中,DSP通過一個串口與CPLD進行通信,串口由數據信號線BDX、幀信號線BFSX以及時鐘信號線BCLKX組成,所有的控制命令和程序數據都是通過這三條信號來傳送的。FPGA器件的CONF_DONE信號線、nSTATUS信號線和nCONFIG信號線均需要用大小為10kΩ的電阻上拉,而nCE信號線則需用10kΩ的下拉電阻。CPLD器件通過nCONFIG信號線和nCE信號線對EPCS配置芯片的控制權進行控制或釋放。當系統上電后,CPLD器件首先對EPCS配置芯片表現為釋放狀態,而FPGA則執行EPCS配置芯片的數據讀取操作,即FPGA的配置過程是:FPGA通過nCSO管腳置EPCS配置芯片的nCS信號線為低電平,并通過ASDO管腳向EPCS發送控制命令和地址,然后在DCLK的上升沿,由配置芯片通過DATA0信號線將配置程序和數據發送到FPGA,在程序發送完畢以后,CONF_DONE由低電平變為高電平,隨后進行FPGA初始化并進入工作狀態。

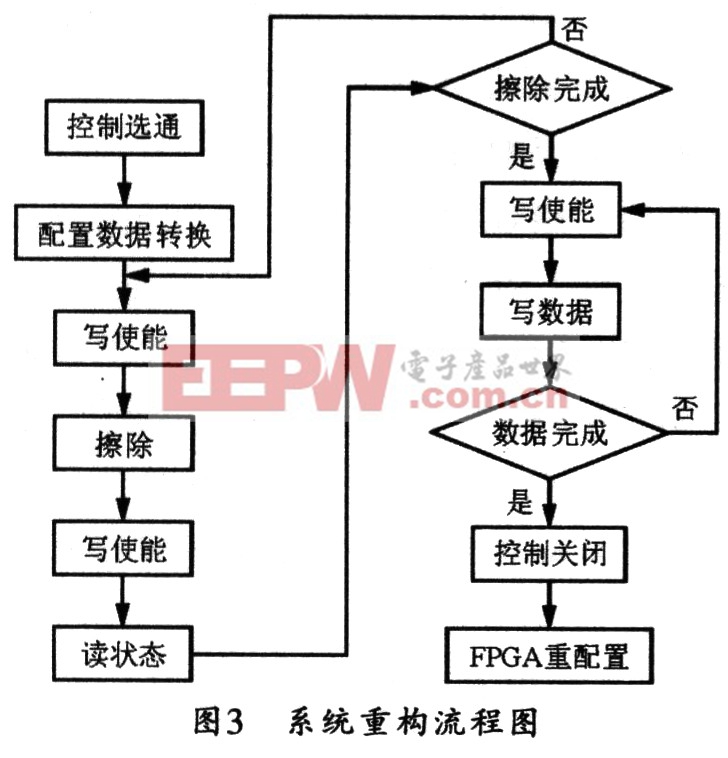

當需要進行系統重構時,可由上位機向DSP器件發送控制命令以進行系統的重構操作。系統重構的流程圖如圖3所示,整個過程包括以下幾個步驟:

(1)上位機發送重構命令后,由DSP通過串口向CPLD器件發送控制選通命令字符串,命令經CPLD器件解析后將nCONFIG信號線置為低電平,并將nCE信號線置為高電平,從而取得對EPCS配置器件的nCS、DCLK、ASDI、DATA管腳的掌控權。此時,FPGA可釋放對EPCS的掌控權,但不讀取EPCS的配置程序數據。

評論