基于FPGA的高速數字相關器設計

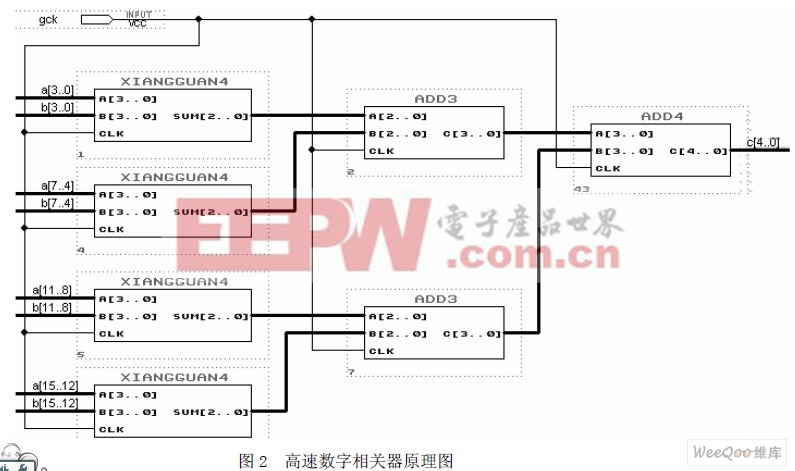

在使用 VHDL進行高速數字相關器設計時,主要實現 4位相關器和多位加法器模塊的設計。其元件生成圖分別是 4位相關器模塊 XIANGGUAN4、3位加法器模塊 ADD3和 4位加法器模塊 ADD4,其電路原理圖如圖 2所示。其中 4位相關器模塊 XIANGGUAN4的主要源代碼為:

entity xiangguan4 is

port(a,b:in std_logic_vector(3 downto 0);

sum:out std_logic_vector(2 downto 0);

clk:in std_logic);

end ;

architecture one of xiangguan4 is

signal ab :std_logic_vector(3 downto 0);

begin

ab=a xor b; --判斷 a,b是否相同

process(clk)

begin

if clk'event and clk='1' then

if ab=1111 then sum=000; --列出各種組合,輸出相應相關值

elsif ab=0111 or ab=1011 or ab=1101 or ab=1110 then sum=001;

elsif ab=0001 or ab=0010 or ab=0100 or ab=1000 then sum=011;

elsif ab=0000 then sum=100;

else sum=010;

end if;

end if;

end process;

end one;

評論