基于SST串行閃存小體積的數據采集系統的設計與實現

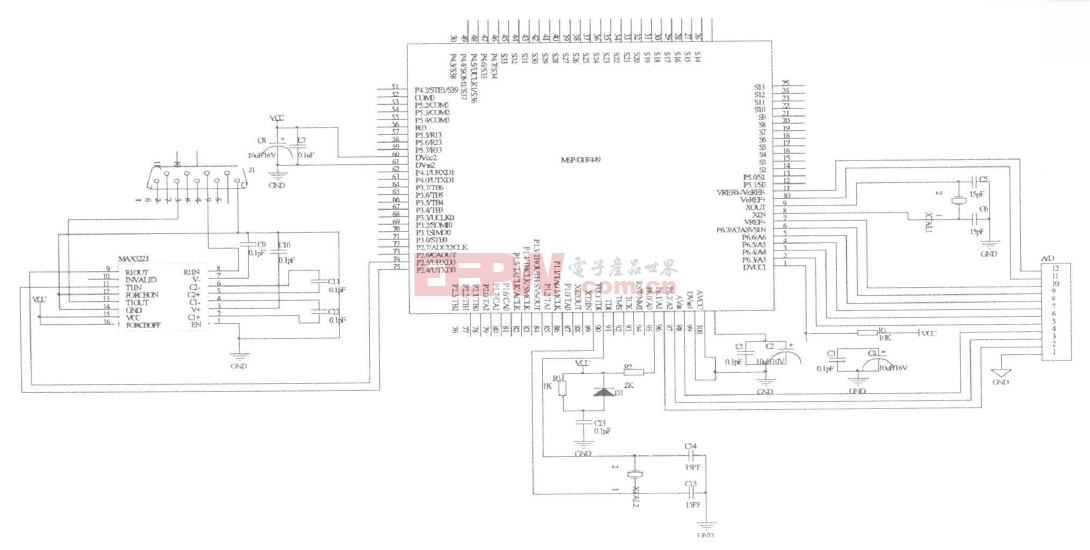

2.1 硬件設計

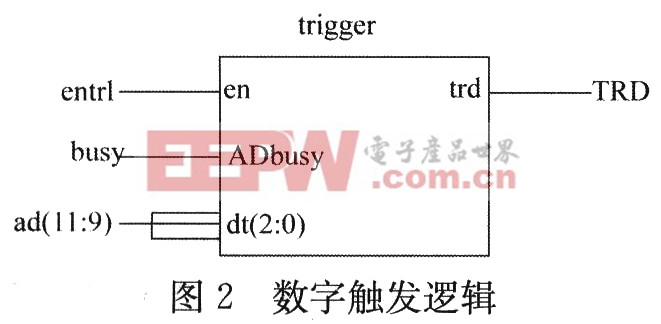

圖2為本系統的數字觸發邏輯圖,在A/D的busy的上升沿,即數據轉化完成的時候檢測數據是否大于設定的觸發值,當轉化的數據連續4次大于設定值時,觸發標志TRD變為高電平。

圖3為CPLD控制閃存并存儲數據的邏輯圖,其中CE、SCK、SI分別用來控制串行閃存的CE、CLK、SI,電路上電后依次往閃存中發送寫使能,寫狀態寄存器,寫使能,配置SO管腳,配置閃存為AAI模式命令,然后等待觸發,觸發后(即TRD為高電平時),AD轉化的數據開時存儲在閃存中。

圖4為地址計數器,用來記錄閃存的存儲地址,即是閃存中存儲數據的大小,在convst的下降沿,計數器加1,當計數器的值等于閃存容量的時候表示閃存已經存儲滿了,然后把tc0置為1,控制電源管理下電,是電路處于低功耗的狀態。

圖5為CPLD控制的總體邏輯圖,時鐘頻率為24 MHz,在本系統中為了能夠更好地提高采樣頻率,采用了2片閃存進行循環采集,CE30、CE31分別控制2片閃存,可以看出上電后,2片閃存同時發送命令,配置閃存為AAI模式,然后A/D轉化的數值連續4次大于設定值時,以后轉化的數據就通過SI存儲在閃存中,由于沒有把TRD作為輸出,所以在邏輯圖中沒有看到TRD變為高電平。

2.2 讀數軟件設計

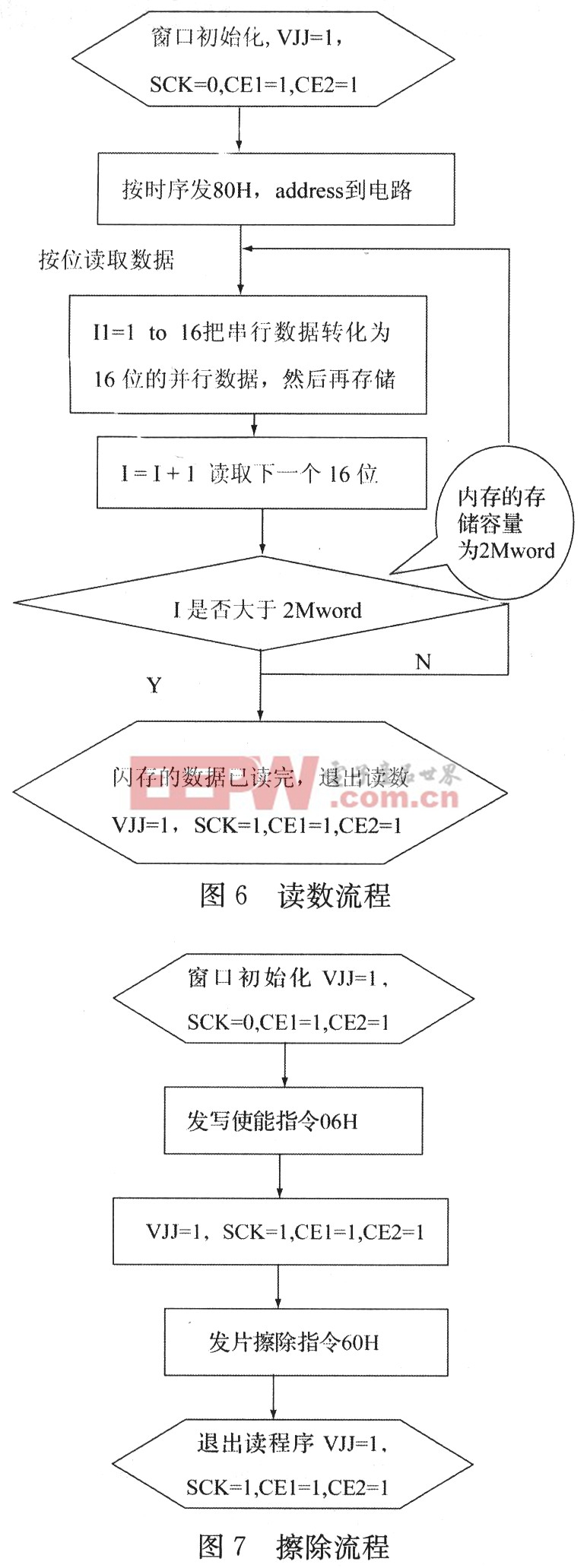

圖6、圖7為閃存的讀數流程和擦除流程。為了在重新上電后能夠讀數和擦除,在插上讀數口后使能CPLD與閃存連接的管腳為高阻狀態,這樣計算機給閃存發閃存命令的時候就不會受CPLD的影響。

3 結束語

本文介紹了一種基于AD、CPLD、串行閃存來實現的小體積的數據采集系統。與其他數據采集系統相比,該系統體積小,存儲器便于控制,易于升級存儲器的容量,能夠滿足一般的信號采集。不足是系統的采樣頻率不夠高,只能達到250 kHz/S,不適于高頻信號的采集。

評論