基于FPGA的AGWN信號生成器

圖4是加法器模塊的仿真波形:因為reset之后的第一個clk上升沿輸出的是PN序列的第二個碼字,第一個碼字在reset同時已經輸出,加法電路是一個組合電路,所以加法器的輸出(addi/addq)在系統剛啟動時不會出現不確定值。

圖5是系統正常運行后乘法模塊的仿真波形。值得注意的是在系統剛開始運轉時,reset信號之后,由于PN序列發生器和加法器中的串行輸出數據,還沒有傳遞到乘法器模塊中的被乘數寄存器(multiregi/multi-regq)和乘積寄存器中,這時從乘積寄存器中串行輸出一些不確定值。

3.2 綜合、布局布線

綜合是指將HDL語言,原理圖等設計輸入翻譯成由與、或、非門,RAM,觸發器等基本邏輯單元組成的邏輯連接,并根據目標及要求優化所生成的邏輯,最后輸出edf或vqm網表文件供布局布線用。

布局布線是將綜合生成的邏輯網表適配到具體器件中,并把工程的邏輯和時序要求與器件的可用資源相匹配,它將每個邏輯功能分配給最好的邏輯單元位置,進行布線和時序,并選擇相應的互邊路徑和管腳分配。

3.3 時序仿真

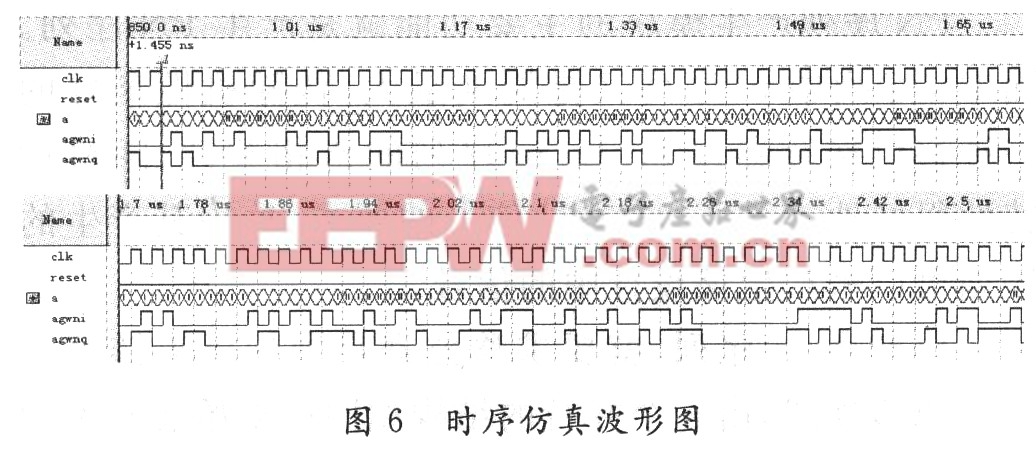

時序仿真也稱后仿真,即通過加入綜合后網表及時延信息對電路進行綜合仿真,速度較慢。前后仿真與綜合、布局布線的關系是一脈相承的,又相輔相成。功能仿真與綜合、時序分析形成一個反饋工作過程,只有過程收斂之后的綜合、布局布線等環節才有意義,孤立的功能仿真即使通過也是沒有意義的,如果在時序分析中發現時序不滿足需要更改代碼,則功能仿真必須重新進行。圖6是在QuartusⅡ中綜合布局布線之后的時序仿仿真波形。由于用了2倍頻電路,所以系統只用了一個時鐘信號clk,a為8位的系數。為觀察產生的AGWN的隨機性,截取的圖形是同一仿真在不同時段的波形圖。

4 結 語

本文使用Verilog硬件設計語言,采用自頂下的設計思路,將整個設計分為了不同的小模塊,分別實現每一個模塊的功能,最終設計出AGWN信號產生的Ver-ilog電路,并實現了功能仿真、綜合、布局布線、時序仿真。該電路實現了在數字通信系統中常用的AGWN信號,由于數字通信系統中用到的是數字信號,可以直接在數字通信系統中加載所產生的數字信號使用。如果需要用到模擬的AGWN信號,可將產生的數字信號通過A/D轉換器轉換為模擬信號再進行使用。

評論