在40G/100G 應用中使用10-Gbps收發器

5

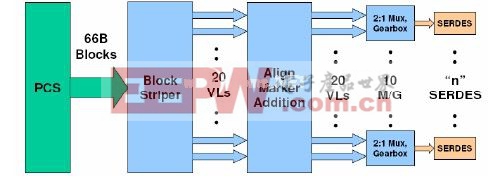

圖7. PCS 通道的發送通路本文引用地址:http://www.104case.com/article/191797.htm

圖8 顯示了 100G PCS 模塊的接收通路。接收通道將數據從10 個( 其中, n=10) 通路解復用至20 個VL。

接收通道去掉VL 偏移,進行對齊,恢復66B 數據流。接收通路上的每個VL 有自己的專用FIFO 緩沖,緩沖深度確定了設計的偏移容限。例如,深度為兩個64 位字的FIFO 緩沖容限達到128 位偏移。

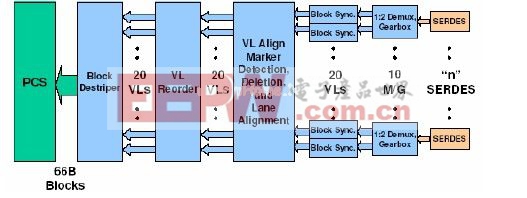

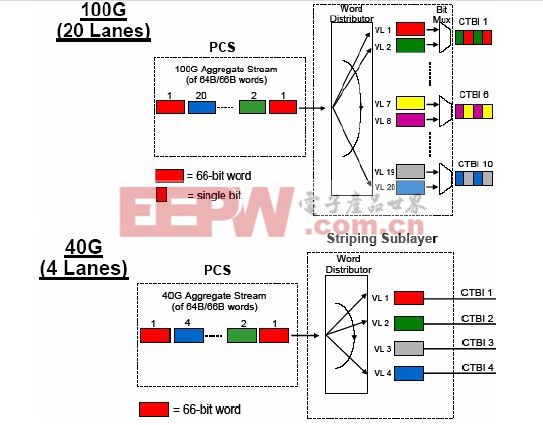

圖9 顯示了VL 的實現,只有當電(n) 和PMD (m) 通路數量不相等時才需要它。當器件收發器通路不對稱時,VL 很容易實現這種轉換。對于100G 實現,基于64B/66B 塊,100G 匯集數據流被分到多個VL 中,對齊模塊在每個VL 中插入。所采用的VL 數量與n 和m 通路的最少公共復用(LCM) 數成比例。實現100G 最多需要20 個VL,實現40G 最多需要4 個VL。虛擬通路支持接收通路進行偏移補償,重新對齊VL,重新組合數據流,匯集為100G 或者40G 數據(64B/66B 塊以正確的順序排列)。

6

圖9. VL 概念

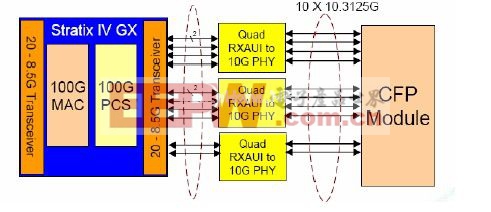

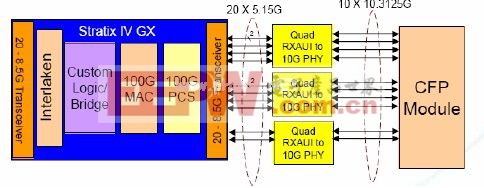

100G MAC 解決方案

如圖10 所示, Altera 的100G MAC 解決方案( 實現 20 個VL) 使用Stratix IV GX FPGA 和外部ASSP 或者定制ASIC 通過RXAUI( 簡化的XAUI 接口,雙倍速率運行) 進行連接,采用了新一代10G PHY 解決方案的MLD 特性。

Altera 公司在40G/100G 應用中使用10-Gbps 收發器

7

圖10. 100G MAC 解決方案

100G MAC IP由Altera合作伙伴MoreThanIP和Sarance提供,符合802.3ba標準。Altera致力于同合作伙伴的密切協作,提供100G 解決方案。

全面的系統解決方案在系統側接口, Stratix IV FPGA 通過20 個數據速率高達6.375-Gbps 的通路,使用Interlaken 協議提供100G 芯片至芯片接口。如圖11 所示,全面的解決方案為線路側至系統側提供專用100G 數據通路。靈活的FPGA 使用戶能夠在系統側使用專用總線接口,連接專用接口和業界標準Interlaken 接口。Altera 的Interlaken解決方案兼容Interlaken Alliance 規范。

圖11. 全面的系統解決方案

這一推薦的解決方案利用了當前的輔助系統和第三方MLD復用PHY來提供40-nm技術節點的業界標準100G平臺。Altera 致力于為100G 網絡平臺的實現提供最佳解決方案。

最佳100G 系統解決方案

圖12所示的最佳100G系統解決方案采用了領先的收發器技術,工作在10 Gbps以上,不需要具有MLD特性的外部 10G PHY 器件。這一方案是真正的單芯片FPGA 100G 解決方案, 100G CFP 光模塊可直接與AlteraStratix IV GT FPGA 連接。Stratix IV GT 器件使用戶能夠在單片FPGA 架構上靈活地采用流量管理、數據查詢

8

版權 2009 Altera 公司。保留所有版權。Altera、可編程解決方案公司、程式化Altera 標識、專用器件名稱和所有其他專有商標或者服務標記,除非特別聲明,均為Altera 公司在美國和其他國家的商標和服務標記。所有其他產品或者服務名稱的所有權屬于其各自持有人。Altera 產品受美國和其他國家多種專利、未決應用、掩模著作權和版權的保護。Altera 保證當前規范下的半導體產品性能與Altera 標準質保一致,但是保留對產品和服務在沒有事先通知時的變更權利。除非與Altera公司的書面條款完全一致,否則Altera 不承擔由使用或者應用此處所述信息、產品或者服務導致的責任。Altera 建議客戶在決定購買產品或者服務,以及確信任何公開信息之前,閱讀Altera 最新版的器件規范說明。

101 Innovation Drive

San Jose, CA 95134

在40G/100G 應用中使用10-Gbps 收發器Altera 公司和數據處理等功能。在目前的產品中, Stratix IV GT FPGA 含有32 個能夠運行在11.3 Gbps 的收發器,另外16 個支持6.5 Gbps 數據速率的收發器( 總共48 個)。

圖12. 最佳100G 系統解決方案

結論

Stratix IV 器件系列滿足了市場對高密度、高性能和低功耗的需求。它是唯一能夠實現最佳40G/100G 解決方案的系列FPGA。在40-nm 工藝節點, Stratix IV FPGA 提供的資源是前所未有的,例如邏輯、片內存儲器和DSP 模塊等。此外, Stratix IV FPGA 支持40G/100G 設計,這些設計需要10G 收發器,要求抖動非常低,以滿足高速設計要求。該器件系列非常適合滿足40G/100G 設計需求,現在已經開始供貨。

致謝

■ Rishi Chugh,產品營銷經理,高端器件營銷, Altera 公司。

■ Seyi Verma,產品營銷經理,高端FPGA, Altera 公司。

評論