低功耗FPGA電子系統優化方法

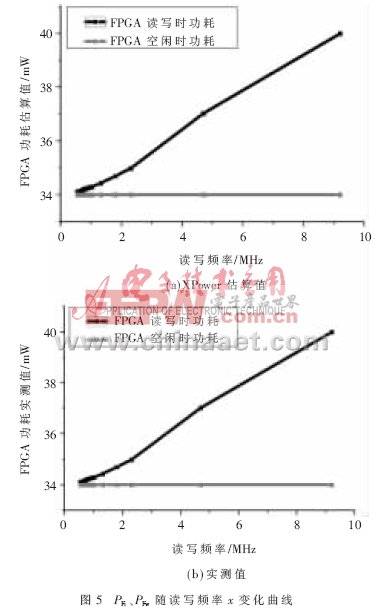

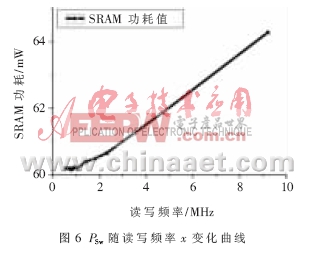

圖5(a)為PFw、PFi的估算值,圖5(b)為測量值,其中黑線為PFw,灰線為PFi。圖6為測得的PSw值。由于y為讀寫時間占空比,所以(1-y)為系統空閑時間占空比,故系統平均功耗P為:

P=(PFw+PSw)?y+PFi(1-y) (2)

又:y=6 kHz/x MHz (3)

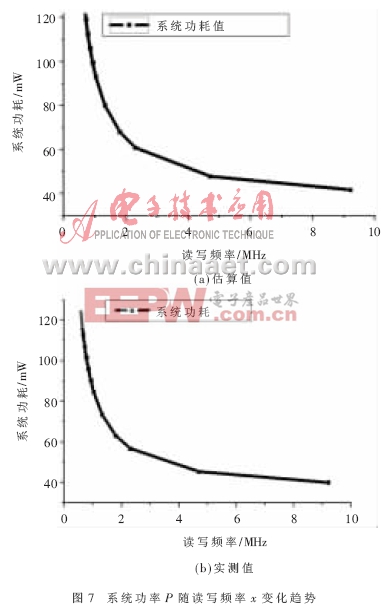

由(2)、(3)式和圖5、圖6中的數據,可得P關于x的曲線圖,如圖7所示。本文引用地址:http://www.104case.com/article/191793.htm

通過對比估算值與實測值發現,估算值與實測值曲線基本吻合,它們的最小點都出現在x為9 MHz處。

由以上結果可知,當讀寫頻率與讀寫時間占空比不同時,系統整體功耗是有差距的。系統采用(9 MHz,6.7×10-4)的參數是最省功耗的,即系統每秒鐘以9 MHz頻率工作6.7×10-4 s,其余時間空閑,比系統用其他讀寫頻率和讀寫時間占空比的平均功耗要小。在所取樣點中,最小功耗值比樣點中的平均功耗值節約了10%左右的功耗,可見此方法在現實設計中可以很好地對系統功耗進行優化。

對電子系統來說,減少功耗可以帶來很多好處,除了簡化系統的散熱處理及系統集成方面的工序、節約成本外,還能提高系統可靠性、降低熱噪聲干擾等。對便攜式儀器、野外工作儀器等電池供電的系統來說,還能延長電池壽命,減少更換電池的麻煩。

評論