如何有效地管理FPGA設計中的時序問題

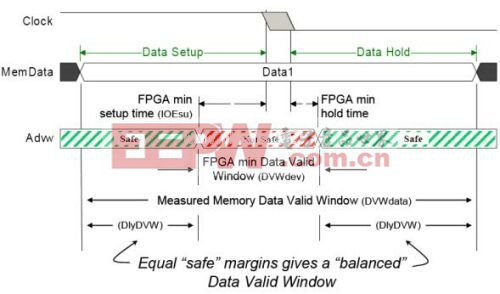

理想的解決辦法是為器件的建立和保持提供一個最大的安全空余,可以通過轉化平衡空余,為二者都提供相同的安全空余。為了平衡空余,我們為接收器件確定最低的有效數據窗口,在實際有效數據窗口的中心窗內可以給我們的存儲器提供設計參數。

利用接收器件最小的建立和保持時間,我們可以利用下面的公式確定最小的安全的有效數據窗口:

最小創建時間+最低保持時間=最低有效數據窗口

如圖3所示,在存儲器器件中可以看出,實際結果是在有效數據窗口中間。為了確保獲取數據,總線必須在接收器最小的有效數據窗口外的安全區域內進行轉換。根據時鐘與數據的關系,信號設計在任一區域內,在獲取數據時,我們確保盡可能多的安全空余。

圖3:平衡實際有效數據窗口中的最小有效數據窗口

實現適當的時鐘偏移

源同步時鐘的相位偏移將有效地改變存儲控制器接收寄存器的最小有效數據窗口,因此將形成平衡有效數據窗口。時鐘偏移調整是FPGA裝置中PLL器件的一個組成部分。要確定偏移的值,我們必須考慮到影響信號的布線延遲和任何外部延遲。

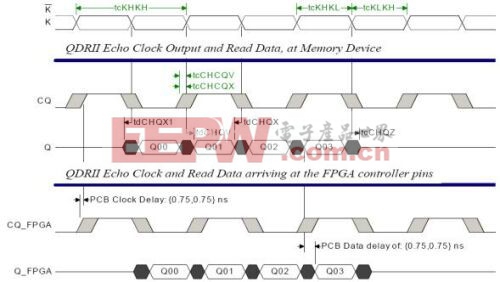

首先,我們使用TimingDesigner軟件通過存儲器數據表為QDR SRAM創造一個圖表(圖4)。我們利用此圖確定存儲器與有效數據窗口中的時鐘和數據信號時序的關系。目的是精確定義存儲器的信號關系,并在PCB到FPGA的設計中傳遞這種關系。

圖4:QDR存儲器讀取時序圖-MT54W1MH18J

從圖4可以看出在FPGA的管腳上,PCB傳播延遲與時鐘(CQ_FPGA)和數據(Q_FPGA)信號間的關系。在TimingDesigner軟件的動態鏈接參數表中使用單獨的變量可以輕松地獲得PCB板的延時及延遲值對相關的信號的影響。現在,我們可以在適當的FPGA裝置中,為獲取時鐘而得到內部布線延遲和確定正確的相位偏移。

四、FPGA設計要素

大多數的FPGA利用約束驅動進行布局和布線。時序約束為關鍵信號提供時序信息。 TimingDesigner軟件提供獨特的時序參考圖如測量和計算變量結果,從行內文字到文件都支持廠商特定的約束語法。例如,在一個FPGA約束布線中,對符合其動態文字窗口的語法要求中,可以通過時序圖中為特定信號計算延遲誤差。然后,我們可以將這些語法通過一個文本文件導入到FPGA的開發系統中,或者我們可以直接將數值復制到FPGA的約束編輯器中。

評論