基于CPLD的函數信號發生器設計

3.3 軟、硬聯調

該系統軟件與硬件之間的聯系不是十分緊密,一般是軟件計算完畢后,將數據存入ROM,CPLD讀取單片機系統的數據,進行運算、邏輯分析,從而產生波形。因此在軟、硬件都基本調通的情況下,系統的軟、硬件聯調難度不大。輸出波形的頻率范圍測試數據如表1所示。本文引用地址:http://www.104case.com/article/191767.htm

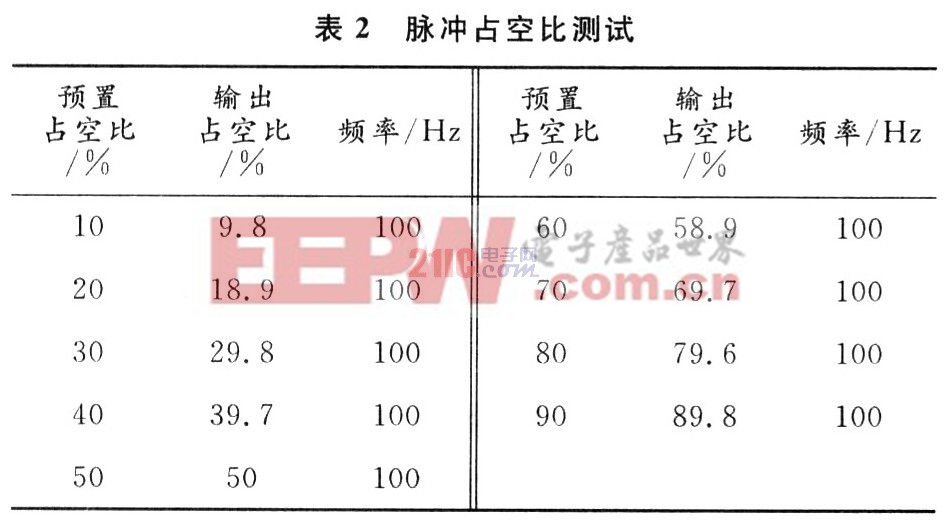

由表1可以看出,在頻率穩定度方面,正弦波、方波、三角波在帶負載的情況下均十分穩定,這正體現了DDFS技術的特點,輸出頻率穩定度和晶振穩定度在同一數量級。脈沖波占空比的調試如表2所示。

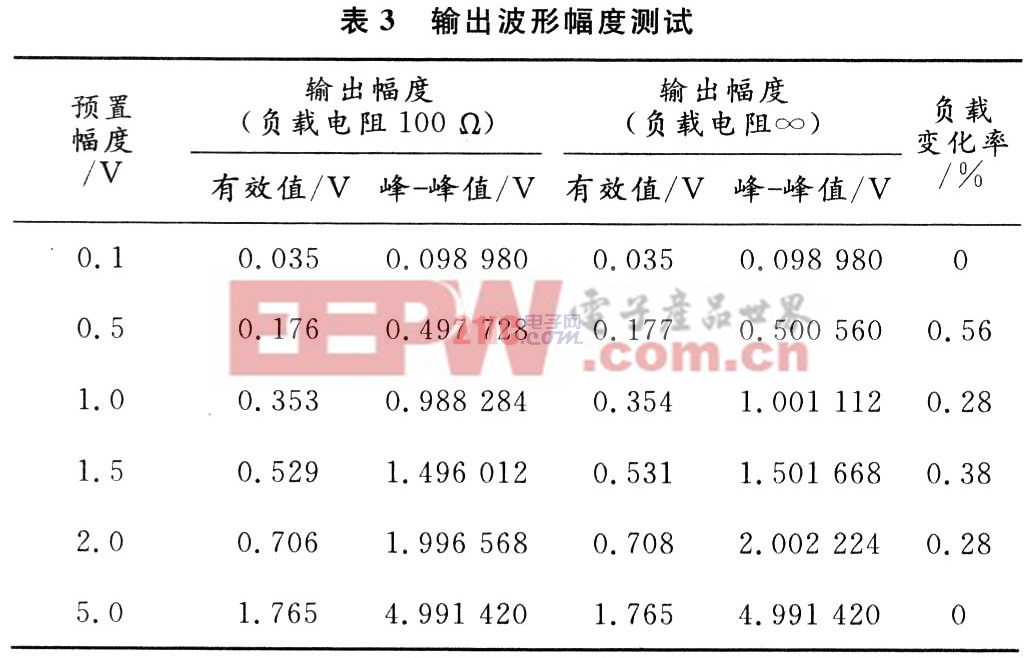

由表2可以看出,占空比可以在10%~90%范圍內預置。在20 kHz正弦波條件下測得的輸出波形幅度數據如表3所示。

由表3可見,電壓穩定度方面,在電壓的絕對值和預置值之差及帶負載和不帶負載的情況下,輸出電壓之差均小于±1/100。

4 結 語

系統采用DDFS技術和單片機控制CPLD的方法,實現了常用的正弦波、方波、三角波和占空比可調的矩形波,頻率范圍為20 Hz~20 kHz。利用LED顯示波形的類型、頻率和幅值,并具有輸出電路保護功能。經實際調試,該系統的頻率范圍寬,步進小,幅度和頻率的精度高。

評論