基于CPLD的函數信號發生器設計

2 系統設計

2.1 總體設計

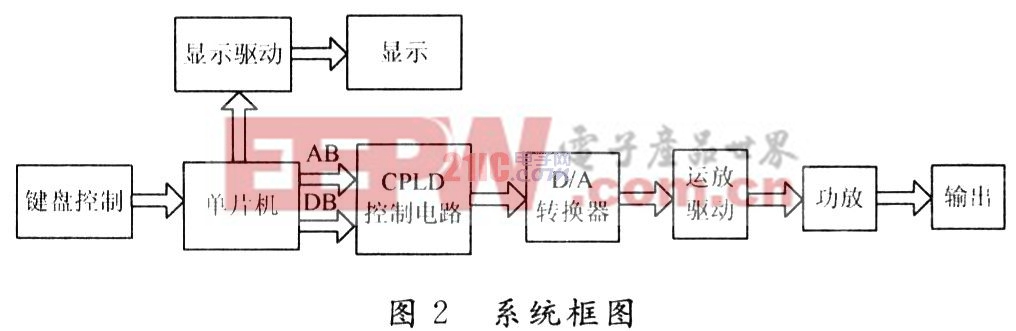

系統框圖如圖2所示。

2.2 主要模塊設計

(1)波形產生電路模塊。用CPLD產生方波、正弦波、三角波和占空比可調的矩形波,從存儲器讀出波形數據,把數據交給D/A轉換器DAC0832進行轉換得到模擬波形。在CPLD內部采用層次化設計方法產生波形,底層采用硬件描述語言描述波形。

(2)鍵盤控制模塊。用單片機80C196接8255芯片控制4×5鍵盤,8255得到鍵盤碼,通過中斷服務程序把鍵盤信息送給單片機。

(3)LED顯示模塊。用8個LED數碼管顯示占空比和頻率值,接口電路簡單,控制方便。LED數碼管的質量輕,體積小,功耗低,接口簡單方便可與8位微處理器或控制器相連。

(4)單片機控制模塊。是系統的主控制器,用于控制其他模塊協調工作。該系統程序的代碼比較長,約幾十KB,使用80C196單片機,片內有ROM,不必擴展外部ROM。

該程序需要較大的RAM,以便進行波形存儲、失真度分析等操作。

2.3 參數計算

頻率參數計算如下:

波形頻率范圍為20 Hz~20 kHz;步進為10 Hz。

因為根據公式:,因此選取的時鐘頻率必須為2 MHz。另外要保證20 kHz以上時,取樣點數都是64點,這樣時鐘頻率必須大于10 MHz。該系統的時鐘頻率采用80 MHz。綜合考慮,相位累加器的時鐘頻率fx根據公式選取,相位累加器位數為16位,頻率步進為。相位增量寄存器為16位,故最高輸出頻率為20 kHz。

D/A轉換器的轉換時間為1μs,可以保證在輸出頻率為1 MHz時,輸出64個樣點。用單片機輸出控制信號與數據,CPLD芯片作為系統實現。

2.4 幅度控制

D/A轉換器是實現幅度可調和任意輸出的關鍵,以此來控制信號發生器的輸出電壓。D/A轉換器中電流的建立時間將直接影響到輸出的最高頻率。該系統采用的是DAC20832,電流建立時間為1μs,在最高頻率點,一個周期輸出64個點,可輸出20 Hz~20 kHz的頻率信號。幅度控制用8位D/A控制,最高峰值為12.7 V,因此幅度分辨率為0.1 V。

2.5 濾波、緩沖輸出電路

D/A轉換器輸出后,正弦波通過濾波電路、輸出緩沖電路對信號去毛刺,使信號平滑且具有負載能力。運放選用高速寬帶運放TL084,截止頻率約為1 MHz,20 kHz以內幅度平坦。

為了保證穩幅輸出,選用OCL功放電路,得到的頻率特性好,波形失真小,具有很強大的電流驅動能力。實際電路測量結果表明,當負載為100Ω,輸出電壓峰值為12 V時,帶寬大于20 kHz,幅度變化小于±1/100。

3 調 試

調試過程分三大部分:硬件調試、軟件調試、軟硬件聯調。電路按模塊調試,各模塊逐個調試通過后再聯調。單片機軟件先在最小系統板上調試,確保外部EPROM和RAM工作正常之后,再與硬件系統聯調。

3.1 軟件調試

該系統的軟件系統很大,全部用80C196來編寫,由于一般仿真器對196的支持都有一定的缺陷,調試比較復雜。除了語法差錯和邏輯差錯外,當確認程序沒問題時,通過直接下載到單片機來調試。采取的是自上到下的調試方法,即單獨調試好每一個模塊,然后再連接成一個完整的系統調試。

3.2 硬件調試

(1)CPLD控制電路的調試。該系統的CPLD采用EPM7128SLC84-15。調試時,使用存儲示波器顯示CPLD的輸出波形,以發現時序與仿真結果是否有出入,便于找出硬件電路中的故障。

(2)高頻電路抗干擾設計。CPLD的時鐘頻率很高。對周圍電路有一定影響。這里采取一些抗干擾措施,如盡量縮短引線,減少交叉,使每個芯片的電源與地之間都接有去耦電容,并將數字地與模擬地分開、敷銅等。實踐證明,這些措施對消除某些引腳上的“毛刺”及高頻噪聲的效果很好。

(3)運算放大器的調試。由于輸出頻率為20 Hz~20 kHz,因此對放大器的帶寬有一定要求,所以在調試濾波電路和緩沖輸出電路時,都選擇了高速寬帶運放TL084。

評論