基于FPGA的圖像裁剪電路的設計與實現

2.2.2 雙端口RAM控制模塊

VGA顯示器要求行像素讀取和顯示同步,由于抽取出來的行列像素在時序上是不連續的,電路必須加存儲器對提取的像素進行緩存。數據緩存模塊可以選用任何存儲單元,根據像素存取的特點,本設計選用了雙端口的RAM對有效像素進行乒乓操作。雙端口RAM乒乓操作的原理如圖3所示。本文引用地址:http://www.104case.com/article/191745.htm

在第N個周期,將輸入的數據流緩存到“數據緩存模塊1”,與此同時,“數據緩存模塊2”中緩存的數據通過“輸出數據流選擇單元”的選擇,送到顯示電路。在第N+1個周期,將輸入的數據流緩存到“數據緩存模塊2”,與此同時,“數據緩存模塊l”中緩存的數據通過“輸出數據流選擇單元”的切換,送到顯示電路。乒乓操作的最大特點是:通過“輸入數據流選擇單元”和“輸出數據流選擇單元”按節拍相互配合切換,將經過緩存的數據流沒有時間停頓地傳送到輸出端,因此非常適合對時序不連續的像素進行流水線式處理。

根據雙口RAM乒乓操作的原理,被抽取出來的像素,一行被緩存的同時,另一行則被順序地讀取出來,保證了像素顯示的連續與同步。雙端口RAM的輸入輸出信號的端口程序如下:

WIRE [29:0] DATA a,DATA b;

WIRE I_a=I;

WIRE I_b=~I;

WIRE[9:0]COIANTER a=(I)?ADDRESSl:COUNlER;

WIRE[9:0]COUNTER b=(!I)?ADDRESSl:COUNTER;

RAM U2(

.DATA a (INDATA),

.WREN a (I a),

.ADDRESS a(COUNTER a),

.CLOCK A(CLK),

.Q a(DATA a),

.DATA b (INDATA),

.WREN b(I_b),

.ADDRESS b(COUNTER b,

.CLOCK B (CLK),

.Q_b(DATA_b));

2.3 VGA顯示控制模塊

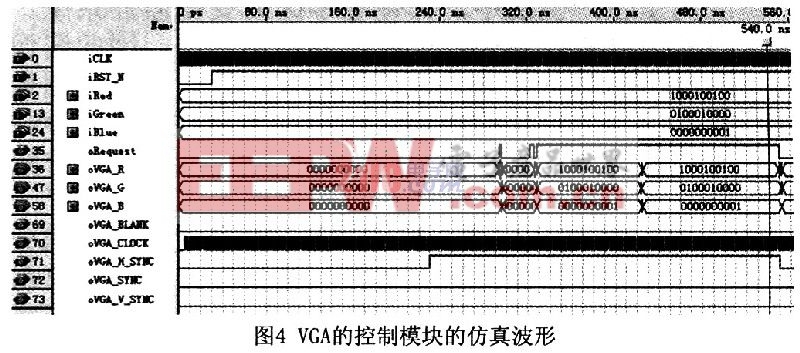

顯示控制器主要用于輸出VGA顯示器所需要的RGB數據信號和控制信號,根據輸入時鐘,顯示控制器可以產生VGA所需要的控制信號,包括場同步、行同步和復合消隱信號等。輸出像素則與輸入像素相同。圖4為VGA的控制模塊的仿真波形。

3 電路調試結果與分析

圖5是分辨率為640×480的原圖像,圖6是分辨率為320×240,比例為4:3的圖像。從處理后的圖像效果可以看出,圖像清晰,信息量豐富,能夠滿足圖像的一般要求。

4 結論

本論文提出了一種基于FPGA的圖像裁剪電路的設計方法,通過改變圖像的分辨率達到壓縮圖像的效果。這種設計方法不僅具備了FPGA開發電路所具有的開發周期短、設計效率高、擴展性和升級性良好、設計靈活等特點,而且與通常所用的插值算法相比,電路結構簡單、設計簡便,從測試的效果來看,圖像清晰,能夠滿足一般圖像的要求。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論