避免PCB設計限制D類放大器性能的實踐設計經驗

輸出濾波

輸出濾波器件務必緊隨其后。從放大器輸出到電感以及從電感到薄膜電容的路徑承載著具有大量高頻成分的大電流,因此該路徑必須盡可能的寬且短,從而減小雜散阻抗和感抗。

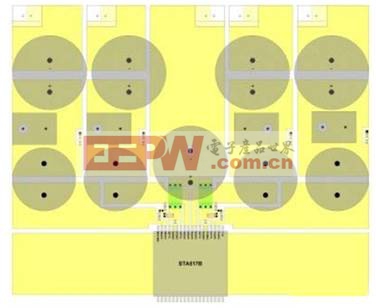

電感和放大器必須盡可能近的放置,同時還要和臨近的電感之間保持一定的距離。如果使用開磁路電感,則為了抑制電磁干擾,這些電感彼此之間至少要有7.5毫米間距,尤其是不同通道之間的電感更應如此。

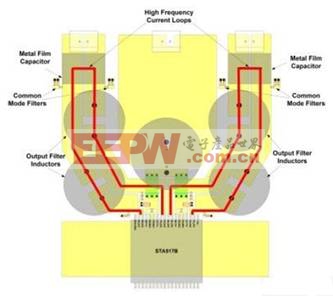

圖8:輸出濾波器件和高頻電流路徑的布局

輸出濾波器件和走線的位置對降低EMI是至關重要的。對低通濾波器而言,走線之間的回路面積須盡可能的小。對單端輸出的放大器來說,放大器的回流路徑就是地,因此回路面積須小。只要電路板上有一個良好的地平面便可實現此點要求。

對于帶有BTL輸出的放大器來說,濾波環路面積是連接IC的走線、濾波電感和薄膜電容之間的面積(見圖5)。為了減小環路面積,BTL輸出濾波的走線必須相互平行且盡可能的保留一定的走線間距。但是,每個獨立通道的輸出走線可以不必彼此相鄰。

低通濾波電容和共模濾波器件必須和電感盡可能的靠近。針對具有單端輸出的放大器,DC阻塞電容必須隨后放置。和揚聲器相連的輸出連接器必須和濾波器盡可能的緊密布局。

圖9:四通道單端放大器輸出布局示例

電路板布局建議總結

器件布局優先級:

1)100nF電源旁路電容

2)1uF電源旁路電容

3)緩沖器件

4)電解電容

5)輸出濾波器件

100nF和1uF去耦電容必須和IC盡可能近的放置。100nF電容和IC之間的間距必須小于2毫米。為了減小走線長度和降低雜散感抗,100nF電容及其與IC的連線必須和IC在電路板的同一層。

100nF電容必須是X7R疊層陶瓷芯片電容(MLC)。1uF電容必須是鉭電容或X7R疊層陶瓷芯片電容。

緩沖網絡必須和IC盡可能近的布局。采用一個額定值至少100V的X7R陶瓷電容,并確保電容能夠處理功率消耗。

從電解電容到IC的電源走線須采用星型連接。

電源和輸出走線必須短且盡可能寬,以便降低雜散阻抗和感抗。

將輸出信號路徑緊密布線,以便減小環路面積;同時保持將濾波器件和IC盡可能近的放置。

在電路板的頂層盡可能多的布局電路,且盡力將電路板的底層作為地平面。只有在萬不得已的情況下才將信號線和電源線走在電路板的底層,而且一定要靈活的使用過孔。

將放大器輸入端的低電壓電路遠離放大器輸出端的電源電路

無論何時都要盡可能的使用表貼器件。SMT器件具有更低的寄生感抗(對旁路電容性能尤為重要)

D類放大器器件需要手工布局布線,不要使用軟件的自動布局布線。

總之,為了降低阻抗和感抗,處理大電流的走線如VCC和輸出信號路徑必須盡可能的寬且短。VCC和輸出信號走線仍具有較高的電壓和電流,因此這些走線必須遠離敏感信號和敏感器件,如時鐘信號和PLL器件。

采用一個完整的地平面

評論