在FPGA中實施4G無線球形檢測器

對4x4矩陣,我們使用了1個對角線單元和7個非對角線單元。分解單個矩陣所花的處理時間為4x4=16個數據周期,而該設計交付數據的速度是每三個時鐘周期一個樣本,因此分解單個矩陣的所用總時長為3x4x4=48個時鐘周期(低于可用的64個時鐘周期)。我們對分解后的矩陣使用了回代法(back substitution),同時以相同的TDM方式進一步進行了重新排序操作。

球形檢測器

球形檢測器采用PED單元進行范數計算。根據樹的層次,我們采用了三種不同類型的PED單元。根節點PED模塊負責計算所有可能的PED。二級PED模塊針對上一級計算得出的8個幸存路徑計算出8個可能的PED。這樣在樹的下一級索引中,我們就有64個生成的PED。第三種類型的PED模塊用于其它樹級,負責計算上一級計算出的所有PED的最鄰近的節點PED。

球形檢測器(SD)的流水線架構可以在每個時鐘周期中處理數據。其結果就是樹的每級只需要一個PED模塊。因此,對4x4 64-QAM系統而言,PED單元的總數為8,與樹的級數相等。

SD可以采用硬解碼和軟解碼兩種類型的解碼技術。硬解碼能夠用貫穿樹的各級的最小距離矩陣度量次序;軟解碼用對數似然比來代表輸出的每個比特。對數似然比一般被當作優先輸入值提供給信道解碼器,比如turbo解碼器。

FPGA資源占用

實施和仿真包括MIMO 802.16e寬帶無線接收檢測過程,但不包括軟輸出生成模塊。目標芯片是Virtex-5 -2FF1738 FPGA。設計的時鐘頻率為225MHz,可用的數據率為83.965MB/s。

表1顯示了設計中每個主要功能單元的資源占用情況。利用率(%)表示FPGA面積占器件總面積的百分比。

表1 按子系統劃分的資源占用情況

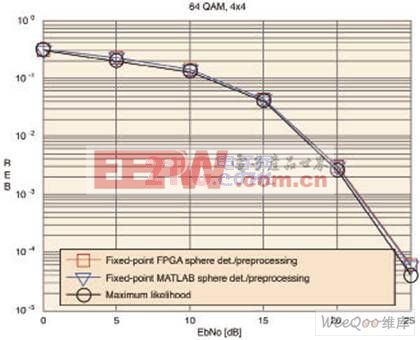

System Generator和基于模型的設計

我們使用針對DSP設計流程的賽靈思System Generator實現了完整的硬判鏈。設計驗證工作不僅使用了MATLAB/Simulink 環境的仿真語義,還有System Generator的協同仿真功能。信道矩陣參數的同相部分和正交部分從正常的分布得出,并由MATLAB交付給System Generator建模環境。我們同樣使用這種仿真框架進行了比特誤碼率計算。圖3對我們的定點硬判決設計BER曲線、浮點硬判決設計BER曲線和最佳ML參考曲線進行了比較。我們通過對賽靈思ML510開發平臺進行基于以太網的硬件協仿真,開發出了該設計的硬件演示。信道矩陣參數采用賽靈思AWGN IP核發送給球形檢測器。我們通過把設計嵌入到自同步BER測試器來計算BER。該儀器能夠向檢測器發送輸入并捕獲誤碼。

圖3 4x4 64-QAM的浮點MATLAB仿真(硬判決)、System

Generator設計(硬判決)BER曲線與最大似然曲線相比

本文就采用空分復用MIMO的通信系統使用的球形檢測器進行了簡要介紹。我們詳細探討了球形檢測器和信道矩陣預處理器的架構情況。實現預處理的方法有許多種,雖然我們的方法在計算上要復雜一點,但得出的BER性能接近最大似然。雖然我們的討論是圍繞WiMAX進行的,設計人員可以把其中的許多方法用于3G/ LTE(長期演進)無線系統

評論