FPGA協處理技術介紹及進展

顯然,FPGA在并行化與流水化方面存在相當大的優勢,同時與GPGPU相比,FPGA在主緩存與帶寬方面也存在優勢。在FPGA中,邏輯資源周圍是存儲器塊。XDI模塊具有一塊帶寬為3.8TB/s的3.3MB主緩存,這是nVidia 8800 GTX型GPGPU上主緩存(支持流處理器)的5~10倍。

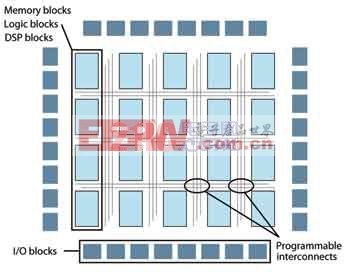

FPGA的優勢還在于,可以利用裕量連接帶寬來靈活構建直達各邏輯塊的數據通道和存儲器訪問通路。圖1所示的可編程互連結構提供了大量的布線帶寬。模塊與電路板可根據FPGA輸出帶寬、存儲器大小及延遲的需要進行設計,I/O端口可由用戶自定義。

圖1 FPGA的架構

最后,FPGA架構還擁有一個優勢,它可擴展為更大型的邏輯塊、存儲器塊與DSP塊的陣列。邏輯與主緩存的大小是一起擴展的。現有最大的FPGA峰值功耗為30W,其FPGA架構有很多空間,可以在不超過現有數據中心功率和冷卻限制的前提下,擴展為新的處理構型。

盡管FPGA架構具有許多出眾的性能,一些性能必須共同發揮作用,才能提供優于CPU協處理的解決方案。

芯片與算法基礎

大部分雙精度浮點算法的加法與乘法操作比例大約為1:1。在FPGA中,加法運算使用邏輯資源,乘法運算使用DSP塊,因此FPGA的邏輯資源與DSP塊的比例必須均衡。FPGA的另一個特點是其可編程功率技術,該技術可針對所有邏輯塊、DSP塊與存儲器塊進行編程,根據設計的時序要求將其設定為高功耗或低功耗模式。

浮點運算核已經改進,可運行于更高的時鐘速率,使用更少的DSP塊和更少的邏輯資源。采用浮點編譯器可減少不同浮點運算核之間用于連接64位數據通路的邏輯資源。

在一次浮點運算結束時,合并對浮點運算進行規格化處理(定點格式轉換至浮點格式)的步驟,可以顯著減少對后續浮點運算輸入的去規格化處理(浮點格式轉換為定點格式)。浮點運算的數學表達式的整個數據通路可熔接在一起,這會最多減少40%的邏輯資源并使時鐘速率略有提高。

浮點運算的正確組合十分重要。如果算法有許多超越運算(求指數、求對數等),FPGA可配置所需要的數目。在GPGPU設計中,會增加一些硬模塊實現上述函數,但比例比單精度浮點邏輯少得多。使用算法技巧、抽象硬件細節及針對個別FPGA資源的優化都需要函數庫。

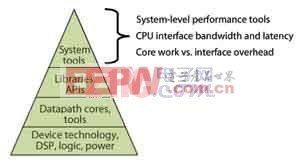

基于芯片、算法與庫基礎,圖2的系統級解決方案涉及到了工具鏈、模塊/板級設計、CPU接口以及采用合作公司專門技術的由CPU至基于FPGA的加速器的數據傳輸。

圖2 FPGA加速系統級解決方案的基礎

評論