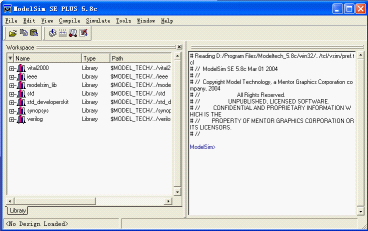

ModelSim和QuestaSim功能簡介及應用

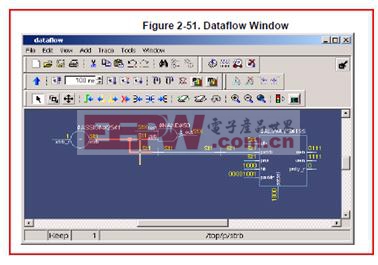

ModelSim Dataflow窗口:

本文引用地址:http://www.104case.com/article/191723.htm

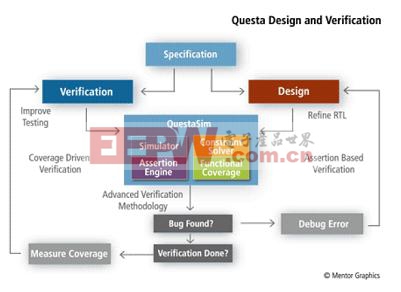

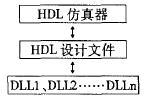

本文引用地址:http://www.104case.com/article/191723.htmQuestaSim是第一個基于標準的單核驗證引擎,集成了一個HDL模擬器,一個約束求解器,一個判斷引擎,功能覆蓋,以及一個通用的用戶界面。

主要特點:

*內建單內核仿真器支持SystemVerilog、verilog、VHDL、PSL以及SystemC。

*內建約束解釋器支持Constrained-random激勵生成,以實現Testbench-Automation;

*支持基于PSL,SystemVerilog語言斷言的功能驗證,支持業界最著名的0-in Checkware 斷言庫功能驗證

*集成化支持功能覆蓋率檢查與分析

*高性能的RTL和Gate-level仿真速度

*支持用SystemVerilog和SystemC實現高層次testbench設計與調試

*高性能集成化的混合語言調試環境加速對混合驗證語言;(SystemVerilog,SystemC,PSL,VHDL,Verilog)的交叉調試與分析

*基于標準的解決方案能支持所有的流程,便于保護驗證上的投資

*提供最高性價比的功能驗證解決方案

Questa AFV提供真正的混合語言驗證

Questa AFV是以混合語言流程 (mixed language flow) 為目標的單核心驗證解決方案,

它同時支持SystemVerilog、VHDL、PSL和SystemC,使設計人員能夠選擇最合適的語言。

除此之外,與SystemVerilog驗證能力的緊密連結,并將其用于受限隨機

(constrainedrandom)測試平臺的產生以及功能覆蓋率的驗證也對VHDL使用者大有好處。

QuestaSim用戶界面與ModelSim類似,命令也完全兼容。

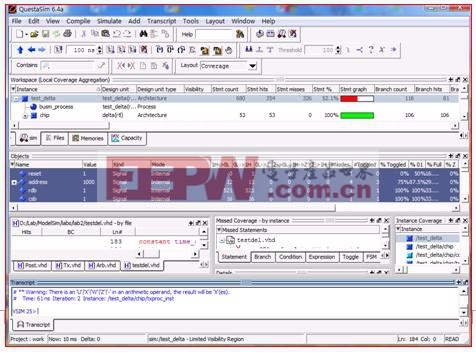

QuestaSim Coverage檢查:

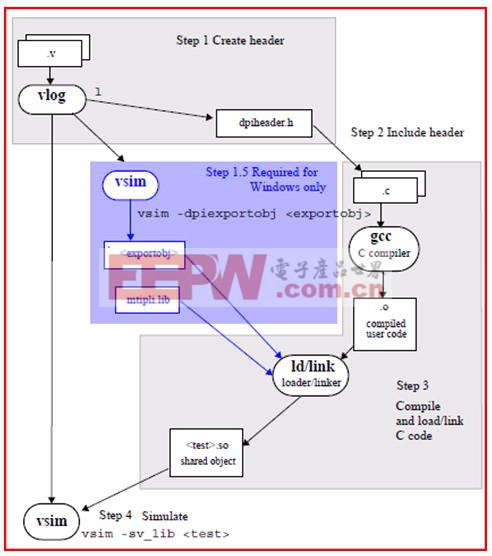

QuestaSim DPI Use Flow:

評論