FPGA的并行多通道激勵信號產生模塊

3.1 結 構

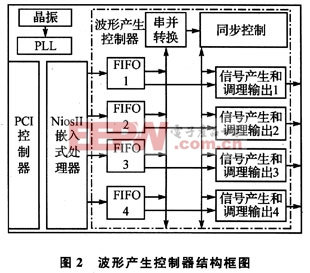

波形產生控制器是整個模塊正常運行的核心,主要完成信號產生控制、信號增益控制以及同步控制。多通道波形產生控制器主要由異步FIFO、同步邏輯與信號產生和調理輸出組成,圖2為波形產生控制器的結構框圖。用戶控制命令經PCI控制器傳輸至Nios II嵌入式軟核后,首先經過譯碼處理,將控制命令按通道進行分類,而后傳輸至波形產生控制器中的異步FIFO進行緩沖。此刻各通道的控制命令主要包括同步命令、信號產生控制字以及增益控制命令,經過串/并轉換后的同步命令控制著通道間的同步時序關系,而信號產生控制字和增益控制字則以并行方式輸出至外圍電路中,完成信號產生和調理輸出。

3.2 實 現

3.2.1 異步FIFO

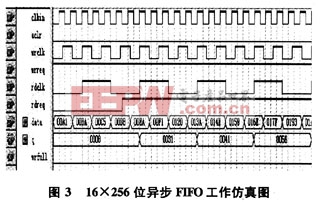

多通道信號產生控制器中具有4個獨立的FIFO,主要用于緩沖PCI控制器與波形產生控制器2個異步時鐘域的數據傳輸,主要包括讀/寫時鐘信號、讀/寫請求信號、數據輸入/輸出信號和空/滿標志位。讀請求信號(rdreq)有效時,在讀時鐘(rdclk)的上升沿處FIFO輸出數據;寫請求信號(wrreq)有效時,在寫時鐘(wrclk)的上升沿處FIFO寫入信號;空/滿標志位決定了數據能夠寫入或讀出,模塊中采用寫滿標志位(wrfull)來表示FIFO內部存儲空間的使用情況。圖3為16×256位的異步FIFO工作仿真圖。

3.2.2 同步邏輯

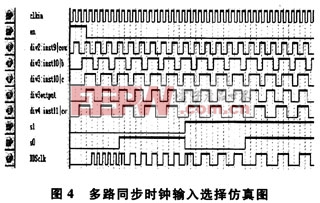

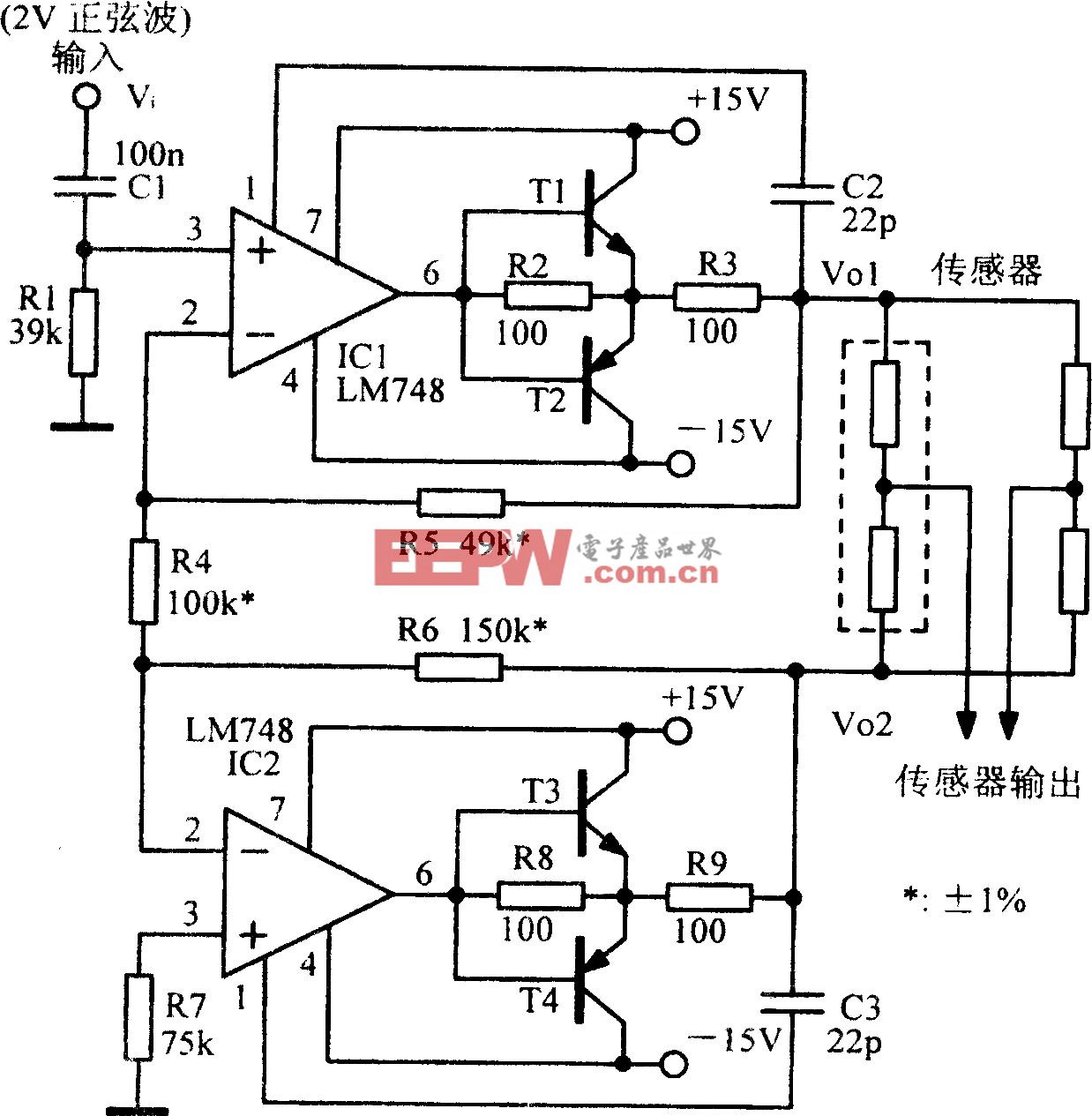

同步邏輯實現多通道波形產生控制模塊的同步控制。信號產生通道的工作狀態有閑置、異步工作和同步工作3種狀態,由用戶提供的同步控制命令決定。當波形產生控制命令加載到輸出寄存器后,在接收到“準備好”命令后同步邏輯控制指定通道同步的輸出控制命令。設計要求各通道具有獨立產生信號的能力,且任意通道間可實現同步操作。首先由同步邏輯產生2分頻、3分頻和4分頻電路分別同步2路、3路和4路的信號輸入,只有1路信號輸出時采用串行時鐘即可。然后根據用戶同步通道控制命令,控制多路選擇通道輸出相應的同步時鐘。采用同步時鐘選擇方法設計的多路同步時鐘仿真圖如圖4所示。

從圖中可見,2位的同步時鐘控制地址s1、s0控制著同步時鐘DDSclk的輸出。當地址位s1和s0分別為00、01、10和11時,同步時鐘DDSclk分別輸出了串行時鐘和串行時鐘2分頻、3分頻與4分頻。其中2分頻和4分頻通過對串行時鐘計數跳轉即可實現,方法簡單且效果良好。對于3分頻的實現則要復雜一點,方法是通過將2個占空比不為50%的3分頻信號相與得到1個占空比為50%的時鐘輸出,如圖中div3:inst10/b與div:inst10/c相與得到的3分頻時鐘輸出div3output。

3.2.3 信號產生和調理輸出

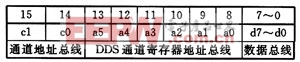

信號產生和調理輸出部分的作用是通過接收控制命令對各通道的DDS電路進行控制。經過FIFO緩沖的16位來自用戶的控制命令FIFO_DATA,由數據控制部分識別、解析、校驗后傳輸到數據串/并轉換模塊,串/并轉換模塊按照數據格式的要求將其轉換為2位通道地址總線部分(c1,c0)、6位DDS寄存器地址總線部分(d5~d0)和8位數據總線部分(d7~d0),組成16位控制字,如下所示:

評論