基于DSP和FPGA的實時圖像壓縮系統設計

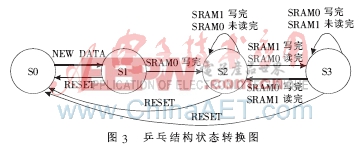

乒乓控制模塊按照功能還分為:S0、S1、S2、S3 4個轉換狀態。其中,狀態S0為初始化狀態(所有信號都處于初始化狀態),系統加電或者復位后進入此狀態;在S1狀態,主要負責對SRAM0的寫入,不可以對SRAM1進行讀操作;在S2狀態,主要負責對SRAM1進行寫操作,對SRAM0進行讀操作,當SRAM1寫完后,如果SRAM0未讀完,則繼續處于狀態S2,如果SRAM0讀完,則進入狀態S3;在S3狀態,主要負責對SRAM0進行寫操作,對SRAM1進行讀操作,當SRAM0寫完后,如果SRAM1未讀完,則繼續處于狀態S3,如果SRAM1讀完,則進入狀態S2。乒乓控制模塊狀態轉換圖如圖3所示。本文引用地址:http://www.104case.com/article/191641.htm

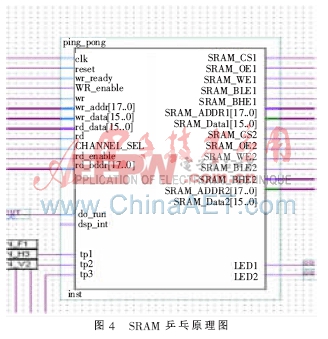

SRAM乒乓電路如圖4所示。圖中,wr_data為Camera Link接口接收到的只包含灰度信號的圖像數據。為了方便圖像數據的管理,每個像素、每行的像素都對應到了SRAM的固定地址,所以wr_addr為該像素在SRAM中的地址,同時也可以表示該像素在一幅圖像中的位置。CHANNEL_SEL為讀SRAM的標志位,0代表SRAM0,1代表SRAM1。

2.3 FIFO緩存模塊和RS422傳輸模塊

由于DSP向RS422模塊傳輸數據并不是勻速傳輸,而且傳輸速度比RS422的傳輸速度快很多倍,所以必須采用FIFO模塊。

3 DSP程序設計

TI公司的TMS320DM642芯片是一款高性能視頻處理器,其主頻可以高達600 MHz,數字處理能力可以達到4 800 MI/ps[3]。

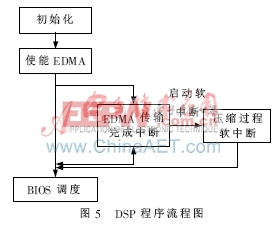

DSP工作流程圖如圖5所示,DSP在相關外設與EDMA相關寄存器初始化完成后,才開始響應中斷事件觸發EDMA傳輸,在本系統中由EXITUINT4中斷上升沿觸發EDMA進行傳輸。在接收到FPGA發送的中斷信號后,開始進行EDMA傳輸,整個EDMA傳輸的過程需要10 ms左右,傳輸完成后觸發EDMA中斷,在中斷服務函數中觸發1個軟中斷,在軟中斷服務函數中進行圖像數據的壓縮。

3.1 EDMA乒乓程序設計

在整個DSP的工作流程中,要實現圖像數據采集、壓縮、傳輸同時進行,則在DSP程序中需要1個雙緩沖buffer,在向buf1中采集圖像信號的時候,DSP可以對buf2中的數據進行壓縮,而在對buf2中進行采集的時候,DSP可以對buf1中的數據進行壓縮。

評論