FPGA架構的功耗(圖)

2 細粒度電源開關

可編程邏輯設計特有的開銷之一是并非所有片上資源都用于給定的設計。可是,未使用的資源保持供電狀態,并以漏電功耗的形式增加了總功耗。模塊級電源開關可分別關掉未使用模塊的供電。每個模塊通過一個電源開關耦接到電源。開關閉合時,該模塊工作。開關斷開時,該模塊從電源有效斷開,從而使漏電功耗降到1/50~1/100。電源開關的粒度可以小到單個CLB和Block RAM。在設計中,這些電源開關可以通過配置比特流進行編程,也可由用戶直接控制或通過訪問端口控制。實際設計的基準測試結果表明,細粒度電源開關可減少漏電功耗30%。

3 深睡眠模式

便攜電子產品的主要要求之一是器件空閑時功耗極低或無功耗。以Xilinx Spartan-3A FPGA為例,該芯片可通過進入休眠模式來達到此目的,這需要外部控制,蘇醒緩慢,且不能恢復FPGA狀態。設計動態控制上述細粒度電源開關,令其關閉所有內部模塊供電,僅保留配置和電路狀態存儲組件為供電狀態。這樣形成的狀態是一種深睡眠模式,其漏電功耗為額定功耗的1%~2%,保存FPGA狀態,退出此模式僅需數微秒。

4 異構架構

電路的最高時鐘頻率取決于其時序關鍵型路徑的延遲。非關鍵型路徑的速度可以較慢而不影響整體芯片性能。在大型系統中,可以有幾個速度關鍵型模塊(如處理器中的數據通路),其他模塊可以是非關鍵型(如緩存)。

當今的FPGA就功耗和速度而言是相同的;每個CLB 均有同樣的功耗和速度特性。異構架構可降低功耗,這種架構包含一些低功耗(同時也較慢)的模塊,方法是在低功耗模塊中實現非關鍵型模塊。這樣做不影響整體芯片性能,因為時序關鍵型模塊并未損失性能。

創建異構架構的一種方法是,分配兩條核心供電軌,即一條高電壓軌(VDDH)和一條低電壓軌(VDDL)。FPGA的每個器件用嵌入式電源開關選擇這二者之一,并相應采用高速度或低功耗特性。設計的詳細時序確定之后,電壓選擇便告完成,所以只有非關鍵型模塊才應以VDDL供電。

創建異構架構的另一種方法是,將FPGA分成不同的區,并將這些區分別預制為具有高速度和低功耗特性。可以用不同電源電壓、不同閾值或通過若干其他設計權衡條件來實現這些區。要避免性能下降,設計工具必須將設計的時序關鍵型器件映像成高速度區,而將非關鍵型器件映射成低功耗區。

5 低擺幅信令

隨著FPGA容量增加,片上可編程互連的功耗越來越大。減少這種通信功耗的一種有效方法是使用低擺幅信令,其中導線上的電壓擺幅比電源電壓擺幅低得多。現今,低擺幅信令常見于在高電容性導線(如總線或片外鏈接)上進行通信的情況。低擺幅驅動器和接收器比CMOS 緩沖器更復雜,所以占用更多芯片面積。但是,隨著片上互連逐漸成為總體功耗的較大組成部分,低擺幅信令的功耗優勢將證明增加設計復雜性是值得的。當然,FPGA用戶不會看到內部信號電壓的差異。

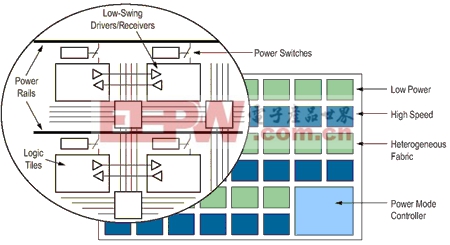

圖3所示為具有上述某些概念的FPGA架構,其可編程異構架構由高速度和低功耗兩個區組成。一個片上功耗模式控制器可管理各種降功耗模式,即深睡眠模式、懸掛模式和休眠模式。在架構內部,可以用專用的供電開關關掉每個邏輯塊的電源。通過布線架構的通信信號流經低擺幅驅動器和接收器,以降低互連功耗。

圖3 具有多種降低功耗解決方案的概念架構

結論

除了目前用于現代FPGA設計的能源優化方案,一些用戶設計決策也可以產生顯著的功耗效益。可以預見,未來的新技術中會有更大膽地遏制功耗的架構解決方案,從而使新的FPGA應用成為可能。

評論