利用FPGA協處理提升無線子系統性能

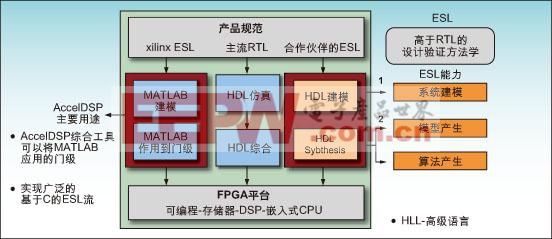

沒有哪一種高級語言或軟件工具能適合當今復雜系統中所見的所有不同單元。語言和設計流程的選擇取決于客戶,有時取決于具體的工程師。因此,Xilinx開發了一套齊全的集成功能,以滿足客戶需求并提供最佳設計環境(見圖3)。

圖3:系統級到 FPGA 設計流程

本文小結

另外,Xilinx正在斥巨資提供一套功能廣泛的高價值IP、電路板和參考設計,以涵蓋射頻卡和基帶應用中的許多關鍵部分,其中包括FFT/iFFT、調制、數字上下變頻和波峰系數的降低電路等。

這一重點舉措的一個例子是開發針對特定無線標準和FPGA架構優化的行業領先的高性能FEC功能,如Turbo編碼器和解碼器。正如我們在分析3GLTE延遲和Turbo解碼器流量要求時所示,FEC功能的硬件加速及其對系統架構的作用在現代無線設備設計中是日漸緊要的當務之需。

雖然一些專家級DSP處理器陸續以嵌入式模塊的形式集成這類功能,但是,從制訂出符合新無線標準的FEC功能參數到形成嵌入式加速模塊出現在硅片中,通常需要好幾個月。一旦實現了嵌入,也還會有遺留的難題,偶爾還會有嵌入式模塊中的功能并非都能按要求工作的局面出現。同時,標準演化迅速,現標準中不時納入一些固定嵌入式模塊不能支持的新要求。

鑒于這些情況,設計人員需要靈活性。他們希望有能力迅捷地開發和部署FEC之類復雜基帶功能,然后根據現場試驗的反饋和標準化工作的進展去修改這些功能。或許他們希望加入自己的專有IP,以便在市場上顯示其解決方案別具一格。正因為是在這種情況下,設計人員不應只考慮某提供商眼下提供的解決方案組合,還應了解這些解決方案是否容易修改以及該提供商能夠提供哪種水平的支持和工具。

評論