一種基于FPGA的鎖相環(huán)位同步提取電路設計

概述

本文引用地址:http://www.104case.com/article/191543.htm同步是通信系統(tǒng)中一個重要的問題。在數(shù)字通信中,除了獲取相干載波的載波同步外,位同步的提取是更為重要的一個環(huán)節(jié)。因為只有確定了每一個碼元的起始時刻,才能對數(shù)字信息作出正確的判決。利用全數(shù)字鎖相環(huán)可直接從接收到的單極性不歸零碼中提取位同步信號。

一般的位同步電路大多采用標準邏輯器件按傳統(tǒng)數(shù)字系統(tǒng)設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統(tǒng)的整體性能。本文給出了一種基于fpga的數(shù)字鎖相環(huán)位同步提取電路。

數(shù)字鎖相環(huán)位同步提取電路的原理

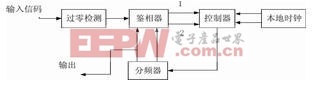

數(shù)字鎖相環(huán)位同步提取電路框圖如圖1所示。

圖1 數(shù)字鎖相環(huán)位同步提取電路框圖

本地時鐘產(chǎn)生兩路相位相差p的脈沖,其頻率為fo=mrb,rb為輸入單極性不歸零碼的速率。輸入信碼的正、負跳變經(jīng)過過零檢測電路后變成了窄脈沖序列,它含有信碼中的位同步信息,該位同步窄脈沖序列與分頻器輸出脈沖進行鑒相,分頻比為m。若分頻后的脈沖相位超前于窄脈沖序列,則在“1”端有輸出,并通過控制器將加到分頻器的脈沖序列扣除一個脈沖,使分頻后的脈沖相位退后;若分頻后

的脈沖相位滯后窄脈沖序列,則在“2”端有輸出,并通過控制器將加到分頻器的脈沖序列附加一個脈沖,使分頻后的脈沖相位提前。直到鑒相器的“1”、“2”端無輸出,環(huán)路鎖定。

基于fpga的鎖相環(huán)位同步提取電路

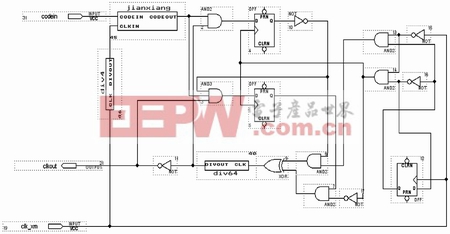

該電路如圖2所示,它由雙相高頻時鐘源、過零檢測電路、鑒相器、控制器和分頻器組成。

圖2 基于FPGA的鎖相環(huán)位同步提取電路

雙相高頻時鐘源

該電路由d觸發(fā)器組成的二分頻器和兩個與門組成,它將fpga的高頻時鐘信號clk_xm變換成兩路相位相反的時鐘信號,由e、f輸出,然后送給控制電路的常開門g3和常閉門g4。其中f路信號還作為控制器中的d1和d2觸發(fā)器的時鐘信號。實際系統(tǒng)中,fpga的高頻時鐘頻率為32.768mhz,e、f兩路信號頻率為32.768/2=16.384mhz。

電路相關文章:電路分析基礎

fpga相關文章:fpga是什么

數(shù)字通信相關文章:數(shù)字通信原理

分頻器相關文章:分頻器原理 鑒相器相關文章:鑒相器原理 脈沖點火器相關文章:脈沖點火器原理 鎖相環(huán)相關文章:鎖相環(huán)原理

評論