基于FPGA的恒溫晶振頻率校準系統的設計

1.5 PicoBlaze軟核設計

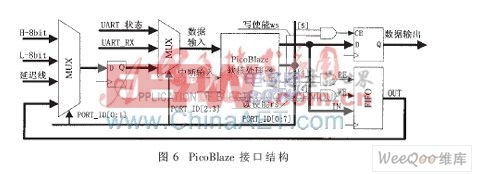

PicoBlaze是XILINX公司設計的8位微控制器軟核,可以嵌入到Cool Runner II、Virtex-E、Virtex-II(Pro) 和 Spartan3(E)的CPLD以及FPGA中,設計靈活方便。PicoBlaze的端口總線提供8位地址(PORT_ID)和讀寫選通信號,最多可以實現256個輸入和輸出端口。接口設計如圖6所示,PicoBlaze用來接收延遲線模塊和計數器模塊輸出的結果,同時讀取異步串行控制器(UART)的數據和狀態信息。其中異步串行控制器直接調用XILINX的IP核,與外部GPS模塊進行串行通信。

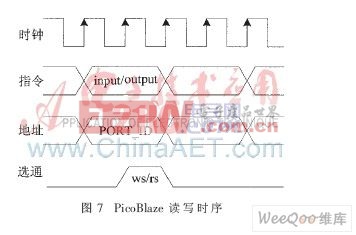

此外,為了實現對測量數據的存儲以方便數據處理,PicoBlaze連接了一個FIFO數據緩沖,用于暫存未處理的測量數據。如圖7所示,PicoBlaze每個讀寫操作需要兩個時鐘周期,此期間地址總線一直處于有效狀態,而讀寫使能信號僅在第二個時鐘周期開始有效,所以地址總線上可以連接適當的邏輯電路進行地址解碼。

設計中使用四路選通器分別連接計數器模塊、延遲線模塊和FIFO緩沖的輸出,其中因計數器模塊中采用16位的計數器循環計數,為了與PicoBlaze輸入匹配,須將計數值分兩部分接到選通器。異步串行控制器的輸出和狀態信息分別接到三路選通器,剩余一路連接四路選通器的輸出。由于UART和PicoBlaze使用的時鐘頻率和測量部分不同,為了提高數據傳輸的可靠性,在選通器之間增加了流水線寄存器。

系統運行時PicoBlaze將對UART狀態進行查詢,當檢測到有GPS串碼數據時便開始讀取其串碼信息。GPS串碼信息用于分析當前GPS的狀態,如果檢測GPS模塊已經鎖定衛星,則系統開始進行測量和校準工作。

2 測量數據處理

根據測量到的時間間隔數據,按照公式:

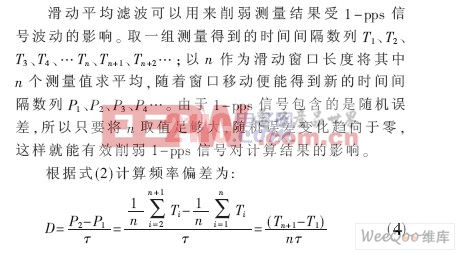

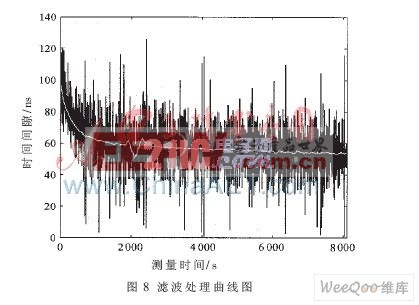

可以計算出晶振信號相對于GPS的頻率偏差,其中T1和T2分別是測量部分相隔采樣時間τ前后輸出的時間間隔測量值。根據頻率偏差的大小,再結合晶振的壓控靈敏度,便可以實現對晶振的輸出頻率進行控制和修正。但GPS信號在傳輸過程中容易受到外界影響,GPS模塊輸出的1-pps信號是一個波動信號,其短期穩定性較差。圖8的黑色曲線是使用本系統測量得到的本地晶振相對于GPS系統的時間間隔曲線,使用這些數據計算得到的頻率偏差也會受到影響而發生波動,所以不能直接使用。

從式(4)可以看出,計算頻率偏差僅僅需要窗口的端點處的測量值而不受窗口內的測量值影響。在實際應用時,計算量很小而且簡單,方便使用PicoBlaze軟核處理器來實現。PicoBlaze連接的FIFO數據緩沖用來存儲滑動窗口中的測量數據。當存儲達到預設的窗口長度時,將從FIFO中順序讀取出先前的測量值,配合當前測量值,根據式(3)計算出頻率偏差。圖8的白色曲線是添加濾波處理后系統輸出的時間間隔,對比可以看出濾波對抖動和較大的跳變點都有很好的抑制作用。

本文介紹的晶振頻率校準系統利用GPS模塊輸出的標準秒脈沖信號對本地晶振頻率進行校準。本設計基于FPGA內部進位邏輯資源實現了高分辨率的時間間隔測量單元,并配合滑動平均濾波法利用PicoBlaze處理器對測量的時間間隔數據進行實時處理。不僅能夠準確地測量本地晶振分頻信號與GPS秒脈沖信號之間的時間間隔,而且降低了GPS秒脈沖波動對測量結果的干擾,為校準晶振頻率提供可靠的修正數據。此外,系統測控部分完全在FPGA中實現,利于提高測量分辨率,減小系統體積,提高系統運行的穩定性。本系統不僅可以用于大地電磁三維采集站,還可以在其他對頻率準確度有要求的儀器中使用。

評論