基于FPGA分布式算法的濾波器設計

2 分布式的濾波器的軟件實現

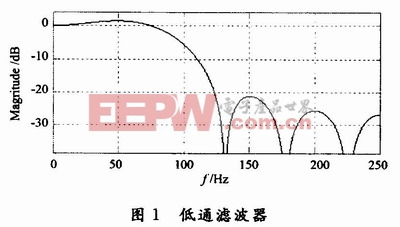

從式(5)和式(7)可以看出,利用分布式算法實現一個N項乘積和,關鍵是如何實現式(4)中乘積項及各乘積項之和。

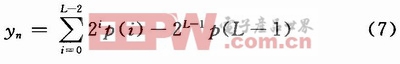

在FPGA中可以預先設定一個N位輸入的查找表來實現部分乘積項,即預先設定N階濾波系統查找表,實現向量x(i)={x0(i),x1(i),x2(i),…,xN-1(i))到p(i)的一個映射。由于查找表的地址空間與階數成指數關系(2N),完全用查找表來實現部分乘積項需要容量很大的存儲器,這就需要占用巨大的資源,而且功耗增加、速度降低。因此為了減小設計規模,可以將一個大的查找表分為幾個較小的查找表來實現。例如,本系統采用的8階FIR濾波器,則用一個查找表來實現需要256(28)位地址空間的ROM,將8階FIR濾波器分成兩個4階FIR濾波器實現,只需要2個16(24)位地址空間的ROM,這樣大大地降低了設計規模和資源使用量。把輸入x(i)作為地址,分為高四位和低四位地址進行查找。表1給出了8階濾波系統的低四位地址x(i)與p(i)的映射關系。本文引用地址:http://www.104case.com/article/191524.htm

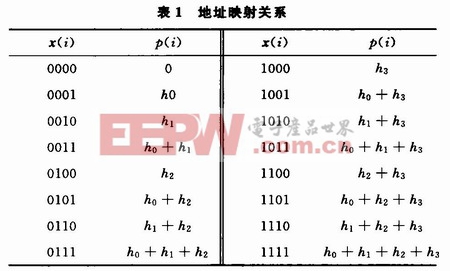

本系統中濾波器系統函數采用Matlab中的fdatool工具,并根據設計要求采用了kaiser窗設計出濾波器的系統函數h(n),其采樣頻率為500 kHz,通頻帶帶寬為100 Hz。設計的低通濾波器如圖1所示。若需實現高通或帶通濾波器,只需在設計時利用高通或帶通濾波器代替低通濾波器即可。

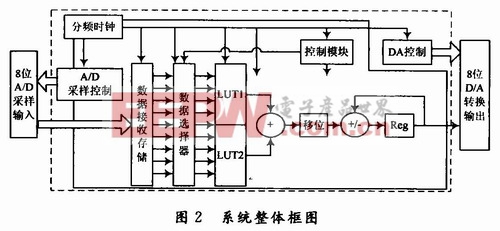

利用Verilog硬件描述語言設計本系統軟件,系統主要分為以下4個部分。包括頂層文件、A/D采樣、算法實現和D/A轉換。系統總體結構如圖2所示。

由于FPGA頻率為100 MHz,采用的ADC0809轉換頻率必須小于1 MHz,所以在頂層文件對系統時鐘進行200分頻,提供外圍所需時鐘。然后對各模塊進行例化,使之成為完整的系統。

評論