基于FPGA和IP Core的定制緩沖管理的實(shí)現(xiàn)

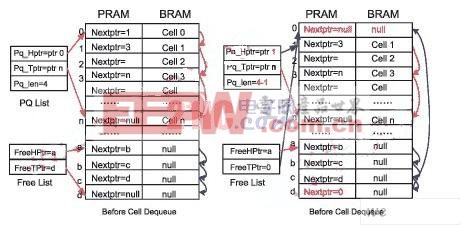

以圖5的讀出操作為例,當(dāng)Read Control模塊由PQ List的首地址0讀出相應(yīng)的BRAM中的內(nèi)容,同時(shí)讀出PRAM中對應(yīng)的下一跳地址1,更新地址1為新的首地址。這時(shí),地址0為已經(jīng)釋放的地址,按空閑隊(duì)列的操作要求,地址0需要進(jìn)入空閑地址隊(duì)列中,在寫操作時(shí)再將地址0讀出提供給Write Control模塊用于寫B(tài)RAM。而基于圖6的結(jié)構(gòu),地址0在被釋放后不再進(jìn)行更新PRAM中的空閑地址隊(duì)列Free List的操作,直接寫入片內(nèi)緩沖中,在Write Control模塊申請地址時(shí)由片內(nèi)緩沖中讀出提供給Write Control模塊 。僅在片內(nèi)Free List緩沖幾乎滿時(shí),進(jìn)行PRAM中的空閑地址隊(duì)列Free List的更新操作,或在片內(nèi)Free List緩沖空時(shí)進(jìn)行PRAM中的空閑地址隊(duì)列Free List的讀取操作。基于圖6的結(jié)構(gòu),在一個讀寫周期內(nèi),可以節(jié)省兩次PRAM的操作,在最壞情況下也可節(jié)省一次PRAM的操作。但基于堆棧的結(jié)構(gòu),棧頂?shù)牡刂繁桓哳l率的反復(fù)的調(diào)用,棧底的地址很難被使用,DRAM的工作壽命會因此受到影響。為保證DRAM的工作壽命,在有些系統(tǒng)中將空閑地址隊(duì)列Free List做成鏈表形式,從而保證每個DRAM的存儲空間都能被平均的使用。讀出操作的Free Lis鏈表結(jié)構(gòu)如圖7所示。

圖7 讀出操作的Free Lis鏈表結(jié)構(gòu)

Read Control模塊由PQ List的首地址0讀出相應(yīng)的BRAM中的內(nèi)容,同時(shí)讀出PRAM中對應(yīng)的下一跳地址1,更新地址1為新的首地址。

Free List相對于堆棧模式增加尾指針d。Free List在回收地址時(shí)維持首指針a不變,將尾指針d更新為剛釋放的地址0,同時(shí)地址d中寫入下一跳指針0。這樣一次BRAM的讀出操作同樣需要一次PRAM的讀取操作及一次PRAM的寫入操作。對于鏈表方式的空閑地址隊(duì)列Free List,在每個讀、寫周期必須進(jìn)行兩次PRAM的寫入操作及兩次PRAM的讀取操作,PRAM的效率不高。

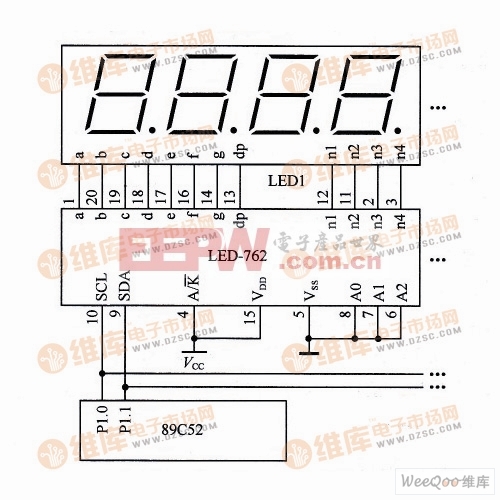

針對兩種空閑地址隊(duì)列的效率及對DRAM的影響,在很多系統(tǒng)中采用了折中的方法,即在PRAM中使用鏈表方法管理空閑地址隊(duì)列Free List,在片內(nèi)采用堆棧模式另建一個空閑地址隊(duì)列Free List,在這種情況下,每個讀、寫周期需要三次PRAM的操作。

在實(shí)際系統(tǒng)中,BRAM的帶寬與PRAM的帶寬一般為TM的瓶頸,PRAM主要受限于訪問的次數(shù),而BRAM受限于接口帶寬。

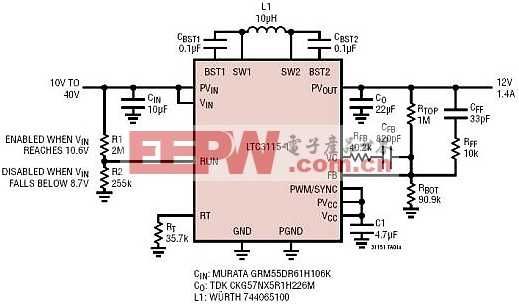

在10G的TM系統(tǒng)中,片內(nèi)數(shù)據(jù)總線的位寬定為128位,系統(tǒng)時(shí)鐘定為150MHz,BCELL的大小定為64B。在這種情況下,讀取操作和寫入操作均為4個時(shí)鐘周期。在滿足10G系統(tǒng)的需求下,讀取、寫入操作周期為7個時(shí)鐘周期。在前面曾計(jì)算過,在滿足10G TM系統(tǒng)的情況下,BRAM采用64位 DDR II SDRAM,接口時(shí)鐘使用250MHz即可滿足數(shù)據(jù)接口的需求。PRAM采用32位ZBT SRAM ,接口時(shí)鐘使用系統(tǒng)時(shí)鐘,每個PCELL為64位,每個讀、寫周期需要6個時(shí)鐘周期完成。在實(shí)際系統(tǒng)中采用Altera FPGA,BM的設(shè)計(jì)可以滿足10G的TM線速工作的需求。

在40G核心網(wǎng)的TM系統(tǒng)中,片內(nèi)數(shù)據(jù)總線的位寬為256位,系統(tǒng)時(shí)鐘采用250MHz(在40GE的系統(tǒng)中可選用200MHz)。采用DDR II SDRAM,接口時(shí)鐘使用333MHz,則192位的BRAM可以滿足40G的TM需求。此時(shí),BCELL可為96B、192B、384B,在這里選用1

92B。當(dāng)BCELL選用192B時(shí),讀取操作和寫入操作同樣均為6個時(shí)鐘周期。在滿足40G系統(tǒng)的需求下,讀取、寫入操作周期為9個時(shí)鐘周期。PRAM采用48位QDR SRAM,接口時(shí)鐘使用150MHz,每個PCELL為96位,在每個讀、寫時(shí)鐘周期內(nèi),PRAM最多可被操作5次。在采用Altera FPGA的情況下,BRAM采用192位 DDR II SDRAM,PRAM采用48位QDR SRAM,BM的設(shè)計(jì)可以滿足40G的TM線速工作的需求。

評論