基于FPGA的寬帶數字接收機變帶寬數字下變頻器設計

4 時鐘重配置模塊

由于FPGA中的多個模塊分別工作在不同的時鐘頻率,當DDC處理帶寬變化時,系統輸出數據率便發生變化,因而各模塊的輸入時鐘頻率也要發生變化。為了實現各模塊輸入時鐘的動態配置,本設計使用了Altera的IP核 PLL的重配置功能(PLL Reconfiguration),并且使用了Altera提供的專門用于PLL重配置的IP核(ALTPLL_RECONFIG),這樣大大降低了整個系統時鐘設計的難度,提高了DDC的靈活性。

5 系統總體調試

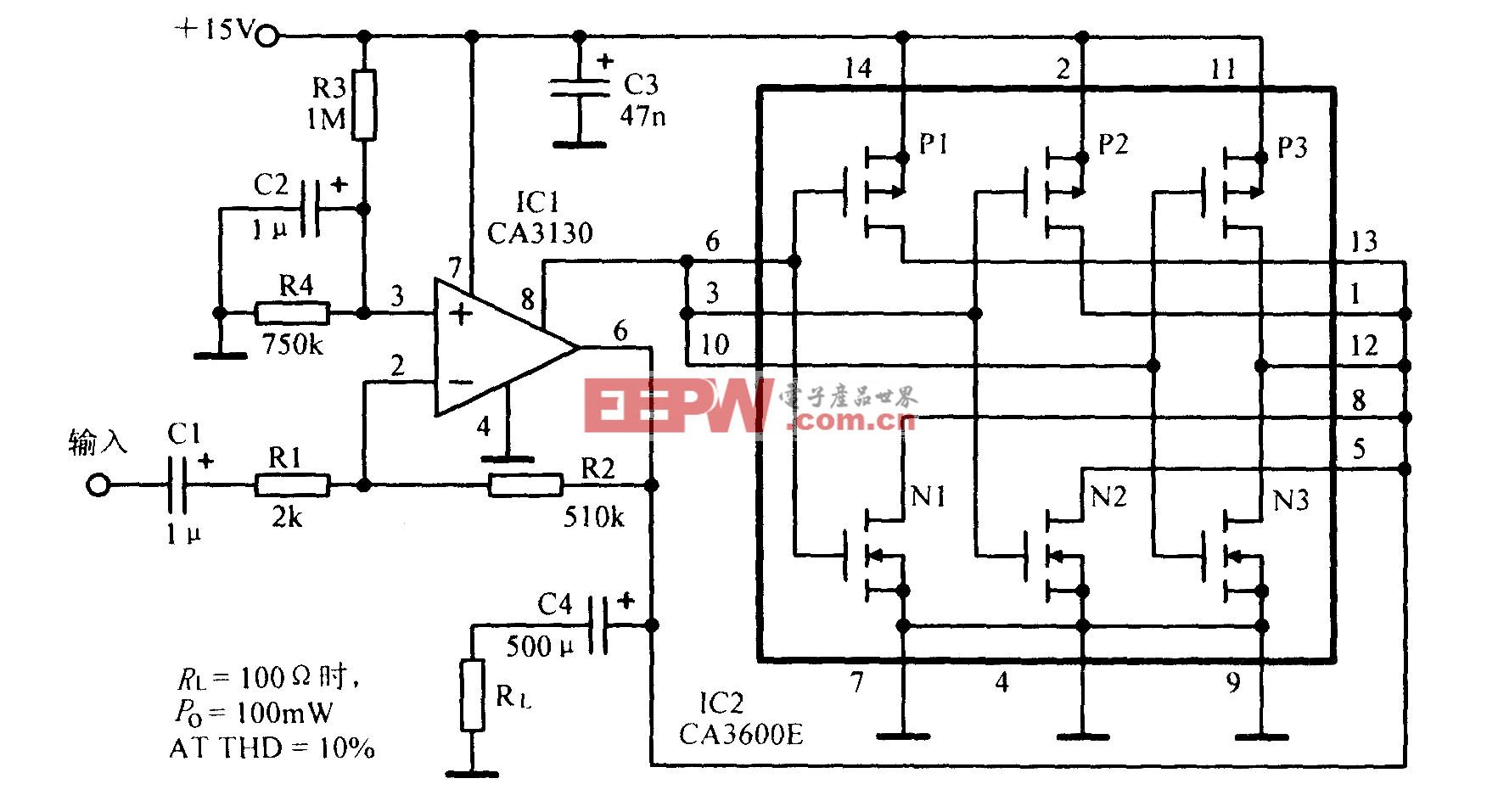

將以上各個模塊按照圖2所示的關系組合在一起,構成FPGA頂層文件。本設計充分利用了EP2S60F672C4上豐富的乘法器資源,使設計的VB-DDC性能達到了最佳。

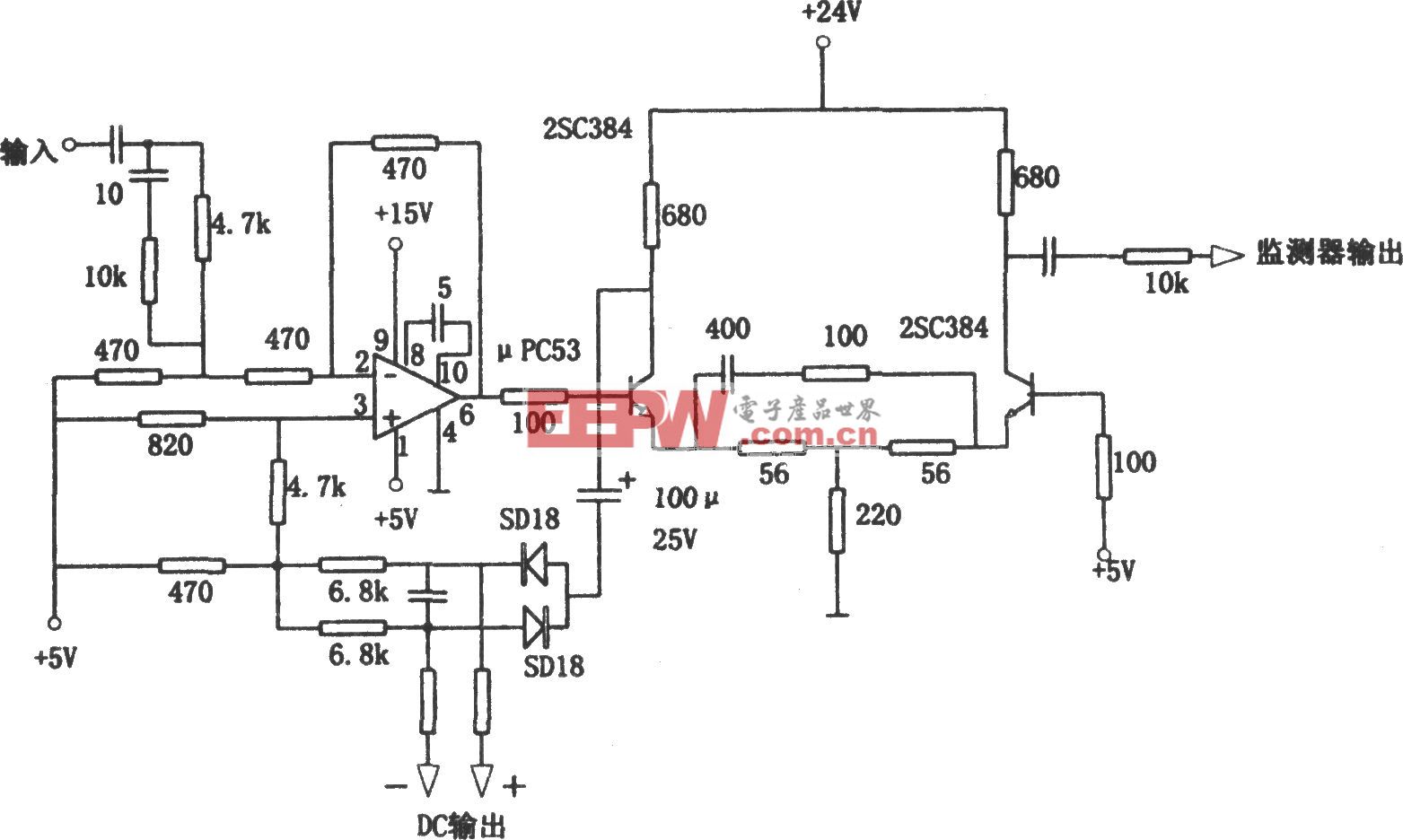

在SignalTap II中對整個VB-DDC系統進行調試的波形如圖6所示。調試時,先在Altera提供的IP核 ROM中存入MATLAB仿真產生的14 bit LFM信號數據,信號帶寬80 kHz,中頻為32.4 MHz,以此模擬AD*5采樣得到的數字中頻信號。

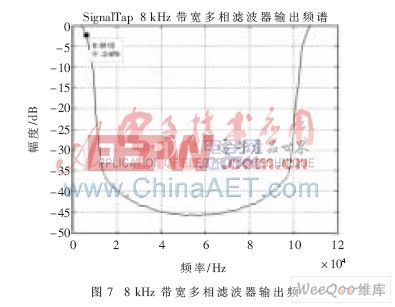

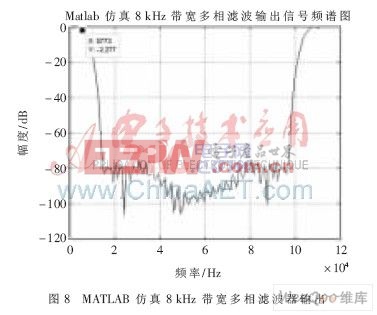

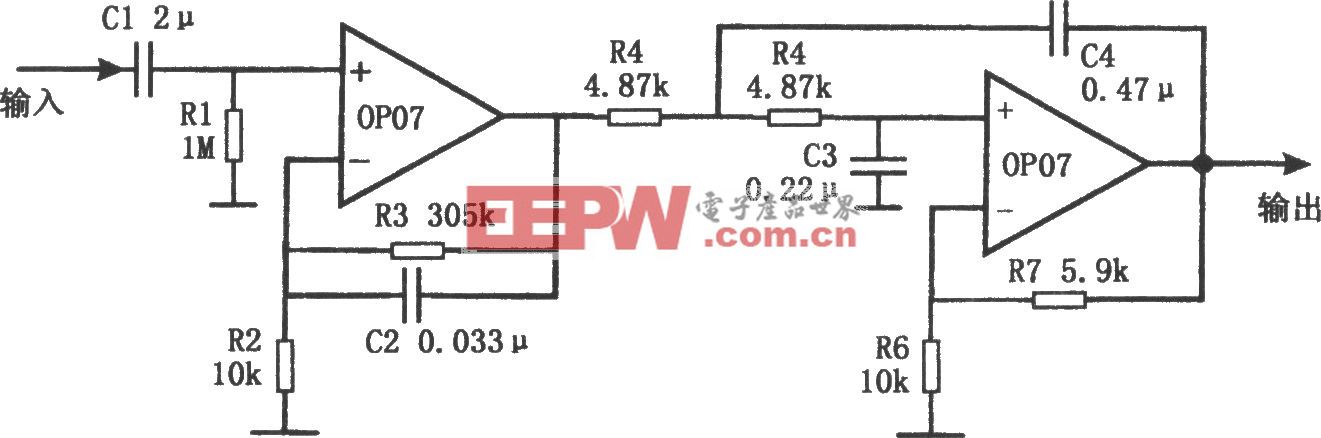

將VB-DDC配置成8 kHz帶寬的基于多相濾波的266階濾波器并級聯在64階FIR濾波器之后,將多相濾波器硬件調試輸出 I_out_F、Q_out_F導入MATLAB進行頻域分析如圖7所示,其與圖8的MATLAB理論仿真結果對比,可得設計滿足要求。

評論