基于FPGA的HD-SDI下變換的研究與設計

2.3 標清SDI并行信號構造處理

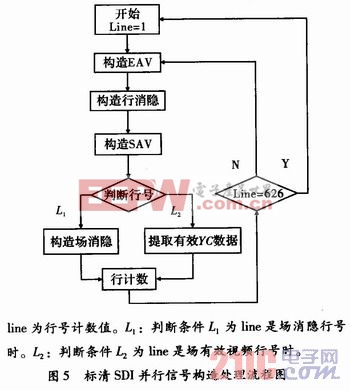

標清SDI并行構造模塊主要是提取標清圖像所要的標清像素點的YC數據,并把數據構造成滿足標清SDI并行分量信號所要求的格式輸出。其處理過程是根據傳輸標清數據所要的27 MHz時鐘來構造標清分量信號中的視頻定時基準碼(有效視頻開始SAV和有效視頻結束EAV)、行消隱數據、場消隱數據。處理過程的流程圖,如圖5所示。

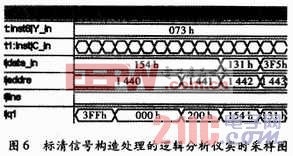

標清SDI并行信號構造處理的邏輯分析儀實時采樣圖如圖6所示。由圖6可以看出Y_in和C_in為高清視頻輸入的并行數據經下變換處理后變成標清視視頻并行數據q1(3FF、000、000、200為第一場有效視頻的起始SAV,154 h和131 h為有效像素點)。圖中line=24為標視頻的第一場中的有效行,data_in為標清構造模塊從YC緩存RAM由相應讀地址addre獲得的有效像素的數據。

3 驗證

本設計通過基于Altera CycloneⅢ系列FPGA芯片EP3C25Q240實驗平臺的驗證。整個實驗驗證平臺結構如圖7所示,視頻信號處理流程簡要如下:我國高清標準HD- SDI信號經過串并轉換芯片變成符合文中設計所要的10 bit的Y分量和10 bit的C分量,高清分量信號進入FPGA進行下變換處理后變成10 bit的時分復用YC的標清視頻分量信號,標清視頻分量信號再串化為SD-SDI信號送給視頻DA板變成普通模擬CVBS視頻信號給電視機顯示。通過 QuanusⅡ自帶的嵌入式邏輯分析儀觀察FPGA中的處理數據,數據符合要求,CVBS視頻信號送給電視機顯示,圖像滿屏顯示,比較清晰且無抖動。

4 結束語

本設計是針對演播室內的HD-SDI信號進行的下變換,直接對圖像信號中的有效像素進行處理,將1 920×1 080(HDTV)視頻SDI流轉換為720×576(SDTV)視頻SDI流,經過上述驗證得出:此下變換設計沒有丟失圖像信號,只是降低了圖像清晰度,且實現簡單,成本較小,易于在工程中實現。對于規模較小的地方數字電視臺實現了高清節目共享,合理地利用了信道資源,節約了擴建高清設備的成本。

本文引用地址:http://www.104case.com/article/191442.htm

p2p機相關文章:p2p原理

評論